调试和测试解决方案

Home > 接口 IP > PCI Express 控制器 IP > 调试和测试解决方案

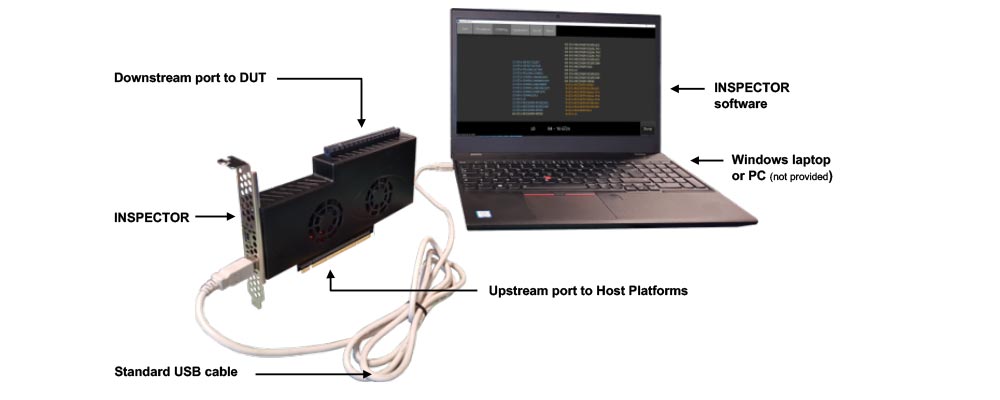

检查器是符合 PCIe 5.0 标准的转接板模块,设计用于 PCIe 设备的非侵入式监控、诊断、运用和调试。检查器使用透明的切换技术在上行端连接到 PCIe 主机平台,在下行端连接到受测试的设备 (DUT)。INSPECTOR 在任一端口上都支持 PCIe 1.x、2.x、3.x、4.x 和 5.0 接口,在最大数据速率下支持高达 4 个通道 (x4)。它通常用于使用在 PCIe 4.0 16 GT/s 速度运行的现有 PCIe 主机在 PCIe 5.0 32 GT/s 速度启动 PCIe 5.0 DUT 并进行诊断测试,但可以在上行和下行端口上支持任何链路速度/宽度组合。检查器的内置诊断功能允许验证工程师立即诊断其 PCIe 设备的问题,而无需昂贵的测试装置。

观看此视频并联如何使用检查器测试和调试 PCIe 5.0 设备

Gen5HOST 提供了对 PCIe 5.0 硬件和软件制作原型和开发的平台。在 Gen5HOST 的核心是在 Xilinx® Virtex® UltraScale+™ FPGA 上运行的 Rambus PCIe 5.0 交换机 IP。Gen5HOST 提供了 PCIe 4.0 x8(上行)到 PCIe 5.0 x4(下行)集成底板,用于开发和验证 PCIe 5.0 端点,还可用于反向配置(PCIe 5.0 上行,PCIe 4.0 下行),用于开发和验证 PCIe 5.0 主机和根复合体。利用 Gen5HOST,PCIe 5.0 设备开发人员可以使用他们选择的操作系统在其生产环境中加速其软件、固件和硬件开发。

Gen5ENDPOINT 是 PCIe 附加卡,适合对 PCIe 5.0 硬件和软件制作原型和开发。在 Gen5ENDPOINT 的核心是在 Xilinx® Virtex® UltraScale+™ FPGA 上运行的 Rambus PCIe 5.0 交换机 IP。Gen5ENDPOINT 包含带有 DMA 和内存映射的 I/O 功能的集成 PCIe 5.0 端点代理程序。利用 Gen5ENDPOINT,PCIe 5.0 主机系统和根复合体开发人员可以使用他们选择的操作系统在其生产环境中加速其软件、固件和硬件开发。

数据中心的发展演变:借助 PCI Express 6.0 实现向 64 GT/s 信令速率的跃进

PCIe 接口是计算机通信系统的重要组成部分,能够通过高带宽以及低延迟性在各个计算节点(如 CPU、GPU、FPGA 和特定工作负载的加速器)之间实现数据的传输。随着 AI/ML 训练等高级工作负载的带宽需求急剧上升,PCIe 6.0 将信号传输速度提升至 64 GT/s,并在标准中做出了一些迄今为止最大的改变。

来自博客

资源

新闻

相关文章

视频

使用检查器测试和调试 PCIe 5.0 设备