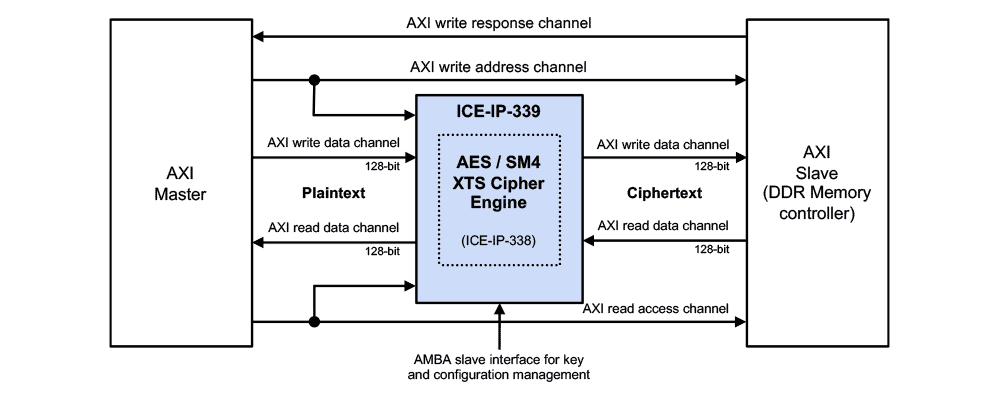

使用 AXI 的 ICE-IP-339 内联密码引擎

现代计算架构必须解决关于芯片外数据保密性的担忧。驱使这些担忧不断增长的主要因素是涉及物理访问内存的攻击,使用零信任的计算架构进行保密计算、监管框架和安全加密资源虚拟化(例如多租户支持等)相关的数据隐私问题。

内联内存加密 (IME) 对于保护芯片外内存(通常是 DDR 内存)中存储的数据至关重要。这也称为保护“使用中的数据”。低延迟加密和解密由一个 IME 引擎处理,该引擎在通过芯片上内存控制器连接到芯片外内存的数据路径中有必需的密码原型。

Rambus ICE-IP-339 内联密码引擎可以无缝集成到客户的芯片上系统 (SOC),以解决 DDR 内存中使用中的数据的安全和隐私担忧。

ICE-IP-339 围绕行业证明的 Rambus ICE-IP-338(内联密码引擎)提供了符合 AXI-4 标准的封装器。这允许 ICE-IP-339 充当读和写 AXI 数据通道上的透明数据处理管道。它在本质上是一个部署 AES/SM4-XTS 密码原型的加密/解密引擎。地址信息从读和写地址通道探听,用作 AES-XTS Tweak 生成的输入。加密处理是基于数据方向将预计算 Tweak 和相应密钥用于必需运行在传入数据上完成的。

ICE-IP-339 支持符合 FIPS-197、IEEE-P1619/D16 和 NIST-SP800-38E 标准,使用 128 和 256 位密钥支持 AES-XTS(以及可选的 SM4-XTS)。ICE-IP-339 交付时配备完全验证的参数化 RTL、定向测试台和 UVM 验证环境。

安全网络基础知识:MACsec、IPsec 和 SSL/TLS/DTLS

MACsec、IPsec 和 SSL/TLS/DTLS 协议是保护移动中(在连通设备之间传达)的数据的主要方式。这些协议可以固定在硬件中,或在软件中作为端到端安全架构的一部分实现。本白皮书提供了有关其中每个协议的基础信息,包括其相互关系和用例。ICE 引擎工作方式

启动时,ICE-IP-339 引擎从 SoC 接收临时密钥,并自动将其转换为合适的密钥以用于加密和解密。

ICE-IP-339 引擎从 AXI4 地址通道探听信息,并以透明方式将其转换为加密引擎的 Tweak 计算输入。具体做法是在读和写地址通道上仲裁。

输入数据时,加密引擎会采用合适的加密运行。具体做法是在读和写 128 位数据通道上仲裁。来自 DDR 控制器的 SoC 读数据意味着解密,来自 AXI 主控的写数据意味着加密。ICE-IP-339 采用 64 字节(= 缓存行宽)和 16 字节数据访问粒度的 XTS 扇区大小。

ICE-IP-339 引擎充当 SoC AXI 总线结构与作为 AXI 从属运行的 DDR 内存控制器之间的 AXI 到 AXI 楔子。它支持标准 AMBA 接口(用于数据路径的 AXI4 和用于密钥管理的 AMBA (APB) 接口),因而支持与标准 SoC 组件无缝集成。IP 的内部构造(例如命令和数据缓冲)可以按 SoC 的需要配置。此外,调试支持信号可促进内部数据流的透明性,因而简化总体系统的总体集成和验证。

MACsec 基本原理

静态(存储在连接设备上)和动态(在连接设备之间传达)的端到端数据安全均应得到妥善保护。对于静态数据,芯片中锚定的硬件信任根是保障所有设备安全的基础。类似地,硬件中基础通信层(第 2 层)锚定的 MACsec 安全性为通过基于以太网的网络传输的数据提供了该信任基础。解决方案产品

性能

- 吞吐量:每周期 128 位(16 字节)宽加密/解密

- 吞吐量:每 4 个时钟周期 1 个 Tweak 计算

- 双向设计,包括读和写请求之间的仲裁

- 在加密(写)和解密(读)之间切换的时钟开销为零

- 30-40 周期数据通道延迟

加密处理

- 算法:AES 或 AES 和 SM4

- 运行模式:XTS

- 支持的密钥大小:128 和 256 位

PPA1

- >1GHz 最大时钟频率

- 区域:50k RefGates,不包括内部加密引擎的区域

- 功耗:0.2-0.4mW/MHz/16B(块)

1参考技术:TSMC 16nm,LVT

接口

- 符合 AMBA AXI4 标准的 128 位和 32 位地址通道接口(用于主和从属集成)

- 符合 AMBA APB 标准的 32 位接口

- 中断和内部缓冲器状态标志

- 调试和内部错误,包括(可选)加密引擎的内部 SRAM 的 ECC

- 归零和重置

合规性

- FIPS 197,IEEE-P1619/D16

- NIST CAVP(要用于符合 FIPS 140-3 标准的产品)

- NIST SP800-38E:AES-XTS

包

- RTL IP

- 驱动程序开发工具包

完整文档

- 硬件集成指南

- 硬件参考手册

工具和脚本

- 用于综合与模拟的 Verilog

- 标准 EDA 工具流所需的所有脚本和支持文件

集成支持

- 完整验证测试台

- 全套测试向量