Home > 接口 IP > Northwest Logic 控制器 > Northwest Logic PCI Express 控制器 > PCIe 5.0 数字控制器

接口 IP

PCIe 5.0 数字控制器

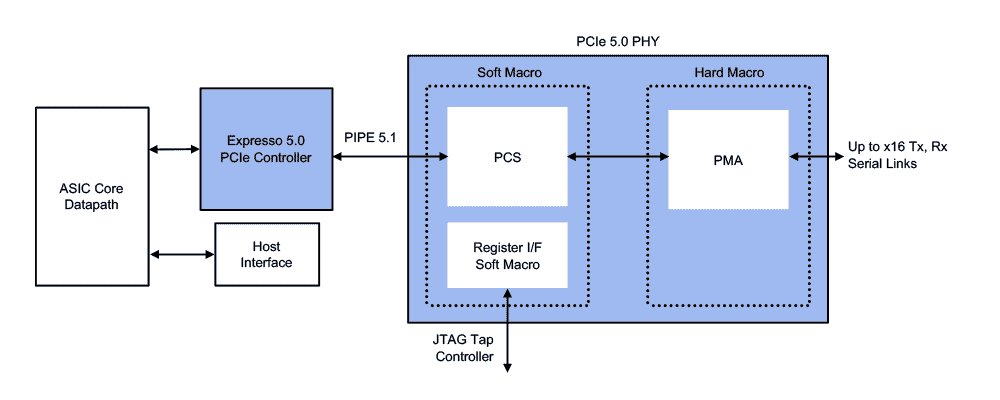

Northwest Logic Expresso 5.0 数字控制器旨在使 PCI Express (PCIe) 5.0 达到最高性能,并提供出色的设计灵活性和集成便利性。它完全向后兼容 PCIe 4.0、3.0 和 2.0。借助 Rambus PCIe 5.0 PHY,其形成了一套综合式接口解决方案,为人工智能 (AI)、数据中心、边缘计算、5G 基础设施和图像处理应用领域的下一代应用提供高带宽和低延迟连通性。

PCIe 5.0 接口的工作方式

结合使用的 Expresso 5.0 数字控制器和 PCIe 5.0 PHY 包含高性能串行链路子系统。我们的 PCIe 5.0 接口解决方案针对富有挑战的性能密集型应用进行了优化,非常适合 AI、数据中心、边缘计算、5G 基础设施和图像处理应用。

Expresso 5.0 数字控制器已通过了与 PCIe 5.0 PHY 的协同验证。PHY 和控制器都支持 PCIe 5.0、4.0、3.0 和 2.0 协议,并且符合 PIPE 5.1 标准。它们可以结合使用,或者与符合 PIPE 5.1 标准的第三方解决方案配对。

PHY 和控制器适用于支持分叉的 x2、x4、x8 和 x16 通道配置。这提高了接口的灵活性,可以支持各种应用。多抽头发送器和自适应接收器均衡支持超过 36dB 的信道插入损耗。

PCIe 5 SerDes PHY 可用于先进的 7nm FinFET 工艺节点。Expresso 5.0 控制器可以在任何工艺中合成。

解决方案产品

特点

可交付成果

服务

特点

- 完整的 SerDes 子系统解决方案,通过了与 PCIe 5.0 PHY 的协同验证

- 符合 PIPE 5.1 标准的接口,可与第三方 PHY 集成

- 支持 PCIe 5.0、4.0、3.0 和 2.0

- x1、x2、x4、x8 和 x16 双通道配置

- 支持 32、16、8、5 和 2.5 Gbps SerDes

- 1-8 物理功能支持

- 支持 SR-IOV,具有最多 255 个虚拟功能端点、根端口、上游交换机端口、下游交换机端口、分叉支持

- 支持 32、64、128、256 和 512 位核心带宽

- 灵活的均衡算法

- 提供了完整事务层 (TL) 部分 TL 和 TL 绕过接口选项

- 全面的诊断和调试状态

- AER、ECRC、MSI-X、MSI、通道反转支持、L1 PM 子状态、SRIS、ECC/奇偶保护

- 经过目标 PHY 充分验证

可交付成果

- 核心(源代码)

- 测试平台(源代码)

- 完整文件

- 专家技术支持

- 维护更新

服务

工程设计服务:

- 定制

- SoC 集成

协议兼容性

| 协议 | 数据速率 (Gbps) | 应用 |

|---|---|---|

| PCIe 2.0 | 5 | 高带宽外围设备和图像处理卡 |

| PCIe 3.0 | 8 | 服务器、存储、联网设备 |

| PCIe 4.0 | 16 | 服务器、存储、联网设备 |

| PCIe 5.0 | 32 | AI、服务器、存储、联网、5G 基础设施 |

SerDes 在 28Gbps 及更高速率下面临信号完整性挑战

随着数据速率超过 28Gbps 达到 56Gbps 甚至更高,保持信号完整性变得越来越困难。在高达 28Gbps 的速率下,由 1 和 0 组成的 NRZ 是首选的标准化编码方案。NRZ 有两个幅度电平,其中在每个符号中包含 1 比特信息,因此也被称为 PAM2(2 电平脉冲幅度调制)。随着串行数据速率达到每个信道 56 Gb/s,带宽增加所导致的信号损伤促使高速串行数据行业采用 PAM4,即 4 电平脉冲幅度调制。

发明

来自博客

资源

新闻

相关文章

视频

![Read PCI Express 5 vs. 4: What’s New? [Everything You Need to Know]](https://www.rambus.com/wp-content/uploads/2020/01/PCI-express-5-Blog-Primer-resource-library.jpg)