支持 CXL 的 PCIe 6.0 重定时器控制器

Home > 接口 IP > PCI Express 控制器 IP > 支持 CXL 的 PCIe 6.0 重定时器控制器

在标称条件下,使用 PAM4 信令速率以 64 GT/s 运行的 PCI Express® (PCIe®) 6.0 链路在标准 PCB 上的触及距离高达 13 英寸。将传输线路由扩展到此距离之外会产生更高的首个比特差错率 (FBER) 并降低链路效率,因为链路恢复和重新传输时间增加了。

随着数据中心部署新的分布式架构,芯片位置需要更大的灵活性,包括需要更长的传输线长度。协议感知重定时器可以完全再生信号,允许电路板设计人员扩展触及范围并灵活地构建各种系统拓扑。Rambus PCIe 6.0 重定时器控制器提供了完整的数字数据路径解决方案,为 PCIe 6.0 重定时器芯片提供一流的延迟、功耗和面积并加快其上市时间。

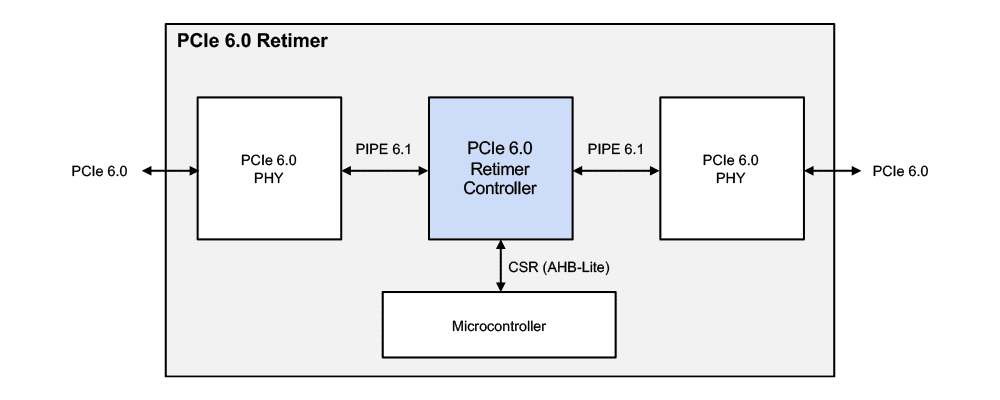

PCIe 6.0 重定时器控制器工作原理

PCIe 6.0 重定时器控制器为信号再生提供了高度优化的低延迟数据路径。它通过 PIPE 5.2/6.1 接口支持重定时器芯片 PHY。控制平面接口通过 CSR (AHB-lite) 提供。PCIe 6.0 重定时器控制器可感知 CXL 协议,并支持使用 PCIe 的 64 GT/s 和更低数据速率的链路。

PCIe 6.0 重定时器控制器为设计人员提供了高度可配置的均衡算法和自适应行为。其高级 RAS 功能支持控制、观测和调试芯片中的控制器和 PHY。此外,它还支持各种 PCIe 时钟架构。

数据中心的发展演变:借助 PCI Express 6.0 实现向 64 GT/s 信令速率的跃进

PCIe 接口是计算机通信系统的重要组成部分,能够通过高带宽以及低延迟性在各个计算节点(如 CPU、GPU、FPGA 和特定工作负载的加速器)之间实现数据的传输。随着 AI/ML 训练等高级工作负载的带宽需求急剧上升,PCIe 6.0 将信号传输速度提升至 64 GT/s,并在标准中做出了一些迄今为止最大的改变。

解决方案产品

PCIe 6.0 重定时器芯片的完整数字数据路径解决方案

- 根据最新的 PCI Express 6.0 (64 GT/s) 设计,并能够支持 32.0、16.0、8.0、5.0 和 2.5 GT/s 链路速率

- 支持 x1、x2、x4、x8 和 x16 链路宽度

- 可感知 CXL 并支持同步报头旁路

- 支持兼容 PIPE 5.2/6.1 的 PHY

- 针对低延迟插入优化的数据路径

- 支持优值和向上/向下 PHY 均衡反馈

- 带自适应行为的高度可配置的均衡算法

- CSR (AHB-lite) 控制平面接口

- 通过预集成的 XpressAgent 调试监控器的高级 RAS 功能

- 支持 SRIS、SRNS 和常见的时钟源模式

- 支持 L0p 节能模式

IP 文件

- Verilog RTL 源代码

- 寄存器的 IPXACT 文件

- C 和 Python 版软件 API,用于

- XpressAgent(调试监控器)

文档

- 重定时器 IP 用户指南

- 入门指南

参考设计

- 可综合 Verilog RTL 源代码

- 模拟环境和测试脚本

- 综合项目和 DC 约束文件 (ASIC)

- Lint 和 CDC 脚本

高级设计集成服务:

- 集成商业和专有 PCIe PHY IP

- 自定义控制器 IP 以添加客户特定功能

- 生成自定义参考设计

- 生成自定义验证环境

- 设计/架构审核和咨询

来自博客

资源

新闻

相关文章

网络研讨会

![Read PCI Express 5 vs. 4: What’s New? [Everything You Need to Know]](https://www.rambus.com/wp-content/uploads/2020/01/PCI-express-5-Blog-Primer-resource-library.jpg)