CCIX 1.1 控制器

Home > 接口 IP > CXL 控制器 IP > CCIX 1.1 控制器

CCIX 1.1 控制器(原名 XpressCCIX)是可配置和可扩展的 PCIe 控制器 IP,专为 ASIC 和 FPGA 的实施而设计。此外,还有一个具有 AXI 的 CCIX 1.1 控制器版本(原名 XpressCCIX-AXI),支持 AMBA AXI 协议规范。

CCIX 1.1 控制器工作原理

CCIX 1.1 控制器 IP 支持 PCI Express 5.0、4.0 和 3.1/3.0 规范以及 PHY Interface for PCI Express (PIPE) 版本 4.x 和 5.x 规范,并支持 CCIX 基本规范修订版 1.1 中定义的 CCIX 扩展速度模式。该 IP 可进行配置,以支持端点、根端口、交换机端口和双模拓扑,以及各种使用模型。

所提供的图形用户界面 (GUI) 向导使设计人员可以通过启用、禁用和调整大量参数,来根据他们的具体要求设定使用该 IP,包括 CCIX ESM 模式、数据路径大小、PIPE 接口宽度、低功耗支持、SR-IOV、ECC、AER 等,以实现最优吞吐量、延迟、大小和功耗。

CXL 2.0 控制器已使用市售和内部开发的 VIP 和测试套件得到广泛验证。它与 Rambus CXL/PCIe 5.0 PHY 集成,以实现完整的 CXL 2.0 接口子系统。或者,它可以与许多第三方 CXL 2.0 PHY 配合使用。

数据中心的发展演变:使用 PCI Express 5.0 加速计算

PCI Express® (PCIe) 接口是计算机通信系统的重要组成部分,能够通过高带宽在各个计算节点(如 CPU、GPU、FPGA 和特定工作负载的加速器)之间实现数据的传输。基于云的计算和超大规模数据中心的兴起以及人工智能 (AI) 和机器学习 (ML) 等高带宽应用,都需要 PCI Express 5.0 的全新性能水平。

解决方案产品

CCIX 1.1 控制器

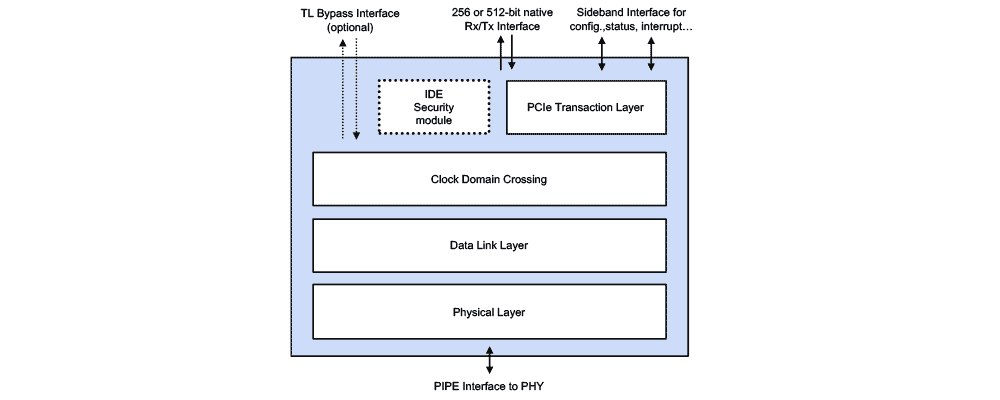

PCI Express 层

- 符合 PCI Express 5.0、4.0、3.1/3.0 标准和 PIPE 4.x(8、16、32 和 64 位)规范

- 符合 PCI-SIG 单根 I/O 虚拟化 (SR-IOV) 规范

- 支持端点、根端口、双模、交换端口配置

- 在 32 GT/s、16 GT/s、8 GT/s、5 GT/s 和 2.5 GT/s 速度条件下支持 x16、x8、x4、x2、x1

- 支持 AER、ECRC、ECC、MSI、MSI-X、多功能、P2P、交叉链路和其他可选功能

- 其他可选功能包括 OBFF、TPH、ARI、LTR、IDO、L1 PM 基底等

CCIX 支持

- 按照 CCIX 基本规范修订版 1.0 实现了 DVSEC 功能

- 支持 CCIX ESM DataRate0 (20 Gb/s) 和 DataRate1 (25 Gb/s)

用户接口层

- 512 位发送/接收低延迟用户接口

- 用户可选择的事务/应用层时钟频率

- PCIe 配置访问、内部状态监控、调试等的边带信令

- 可选事务层旁路

完整性和数据加密 (IDE)

- 实现 PCI Express IDE ECN

- 可配置的 IDE 引擎

- 支持 x1 到 x16 通道

- PCIe IDE 采用 256 位或 512 位数据总线

- 支持控制和滑动模式

- 支持提前终止 MAC

- 支持多流

- 利用高性能 AES-GCM 进行加密、解密、验证

- 1、2、4、8 个 TLP 的 PCIe IDE TLP 聚合

- PCIe IDE 自动 IDE 前缀插入和检测

- PCIe IDE 自动 IDE 同步/失败消息生成

- PCRC 计算和验证

- 高效键控/刷新

- 旁路模式

独家特点和功能

- 内部数据路径大小基于链路速度和宽度自动扩展或缩减(64、256、512 位),减少门数并实现最优吞吐量

- 可动态调整的应用层频率,低至 8Mhz,以改善节能

- 可选的 MSI/MSI-X 寄存器重映射到内存,在实现多功能或 SR-IOV 时减少门数

- 利用可配置的管道,可以在 Intel 和 Xilinx FPGA 上全速运行,使用相同的 RTL 代码时完全支持高达 Gen4 x8、Gen3 x16、CCIX 25G x8 的生产 FPGA 设计(在支持时)

- 超低发送和接收延迟(不包括PHY)

- 接收端(接收流)和发送端(合并重播/发送缓冲器)智能缓冲器管理支持更低的内存占用

- 高级可靠性、可用性、可维护性 (RAS) 功能包括 LTSSM 定时器覆盖、ACK/NAK/重播/UpdateFC 定时器覆盖、解码的 PIPE 接口访问、接收和发送路径上的错误注入、恢复详细状态等,允许在任务关键型 SoC 中安全可靠地部署 IP

- 可选的事务层旁路允许客户开发的应用层

- 可选的 QuickBoot 模式允许链路训练速度提升至 4 倍,将系统级别模拟时间缩短 20%

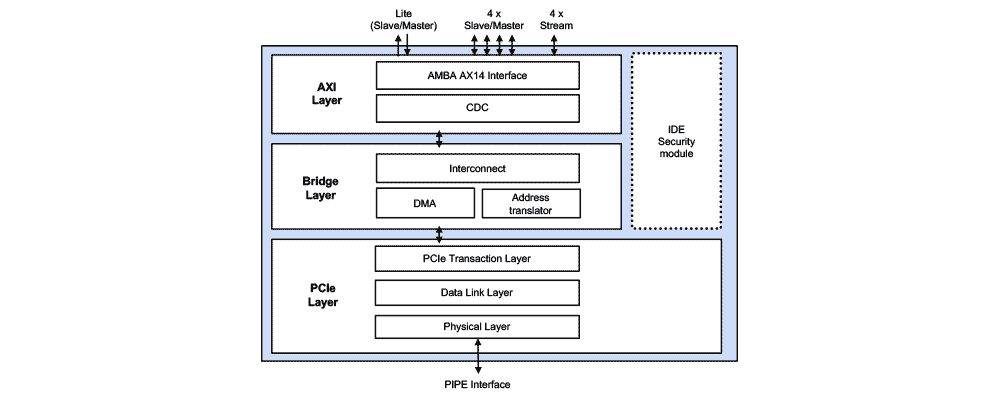

具有 AXI 的 CCIX 1.1 控制器

PCI Express 层

- 符合 PCI Express 5.0、4.0 或 3.1/3.0 标准和 PIPE(8、16、32 和 64 位)规范

- 符合 PCI-SIG 单根 I/O 虚拟化 (SR-IOV) 规范

- 支持端点、根端口、双模配置

- 在 32 GT/s、16 GT/s、8 GT/s、5 GT/s 和 2.5 GT/s 速度条件下支持 x16、x8、x4、x2、x1

- 支持 AER、ECRC、ECC、MSI、MSI-X、多功能、P2P、交叉链路和其他可选功能

- 支持许多 ECN,包括 LTR、L1 PM 基底等

CCIX 支持

- 按照 CCIX 基本规范修订版 1.1 实现了 DVSEC 功能

- 支持 CCIX ESM DataRate0 (20 Gb/s) 和 DataRate1 (25 Gb/s)

AMBA AXI 层

- 符合 AMBA® AXI™ 协议规范(AXI3、AXI4 和 AXI4-Lite)和 AMBA® 4 AXI4-Stream 协议规范

- 支持用户可选择的多个 AXI 接口,包括 AXI 主、AXI 从属、AXI 流

- 每个 AXI 接口数据宽度可独立配置 256、128 和 64 位

- 每个 AXI 接口可在单独的时钟域中运行

完整性和数据加密 (IDE)

- 实现 PCI Express IDE ECN

- 可配置的 IDE 引擎

- 支持 x1 到 x16 通道

- PCIe IDE 采用 256 位或 512 位数据总线

- 支持控制和滑动模式

- 支持提前终止 MAC

- 支持多流

- 利用高性能 AES-GCM 进行加密、解密、验证

- 1、2、4、8 个 TLP 的 PCIe IDE TLP 聚合

- PCIe IDE 自动 IDE 前缀插入和检测

- PCIe IDE 自动 IDE 同步/失败消息生成

- PCRC 计算和验证

- 高效键控/刷新

- 旁路模式

数据引擎

- 可选内置旧版 DMA 引擎

- 高达 8 个 DMA 通道,Scatter-Gather,描述符预取

- 完成重排序、中断和描述符报告

- 直接 PCIe 到 AXI 和 AXI 到 PCIe 通信的可选地址转换表

独家特点和功能

- 内部数据路径大小基于链路速度和宽度自动扩展或缩减(64、256、512 位),减少门数并实现最优吞吐量

- 可动态调整的应用层频率,低至 8Mhz,以改善节能

- 可选的 MSI/MSI-X 寄存器重映射到内存,在实现多功能或 SR-IOV 时减少门数

- 利用可配置的管道,可以在 Intel 和 Xilinx FPGA 上全速运行,使用相同的 RTL 代码时完全支持高达 Gen4 x8、Gen3 x16、CCIX 25G x8 的生产 FPGA 设计(在支持时)

- 超低发送和接收延迟(不包括PHY)

- 接收端(接收流)和发送端(合并重播/发送缓冲器)智能缓冲器管理支持更低的内存占用

- 高级可靠性、可用性、可维护性 (RAS) 功能包括 LTSSM 定时器覆盖、ACK/NAK/重播/UpdateFC 定时器覆盖、解码的 PIPE 接口访问、接收和发送路径上的错误注入、恢复详细状态等,允许在任务关键型 SoC 中安全可靠地部署 IP

- 可选的事务层旁路允许客户开发的应用层

- 可选的 QuickBoot 模式允许链路训练速度提升至 4 倍,将系统级别模拟时间缩短 20%

IP 文件

- Verilog RTL 源代码

- 功能模拟的库

- 配置助手 GUI

文档

PCI Express 总线功能模型

- 加密模拟库

软件

- PCI Express Windows x64 和 Linux x64 设备驱动程序

- PCIe C API

参考设计

- 可综合 Verilog RTL 源代码

- 模拟环境和测试脚本

- 综合项目和 DC 约束文件 (ASIC)

- 支持的 FPGA 硬件平台 (FPGA) 的综合项目和约束文件

高级设计集成服务:

- 集成商业和专有 PCIe PHY IP

- 自定义 PCIe PCS 层的开发和验证

- 自定义控制器 IP 以添加客户特定功能

- 生成自定义参考设计

- 生成自定义验证环境

- 设计/架构审核和咨询

来自博客

资源

新闻

相关文章

视频

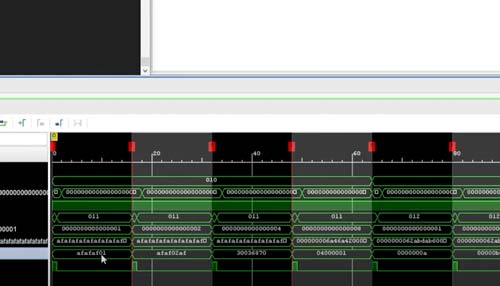

基于 FPGA 的设计上的 CXL 互连演示