Home > 接口 IP > SerDes PHY > 56G SerDes PHY

56G 工作原理

Rambus 56G MPS PHY 是一款符合 PAM-4 和 NRZ 标准的 IP 解决方案,可在具有挑战性的长距离数据中心环境中提供可靠的性能。直接集成到架构中的 28 GS/s ADC 实现了未来的可扩展性和扩展范围。凭借高性能和多协议兼容性,PHY 在插入损耗超过 35dB 的铜缆和背板信道中支持 9.95 – 58 Gbps 的数据速率。通过控制 PHY 的功耗实现了灵活的系统设计。

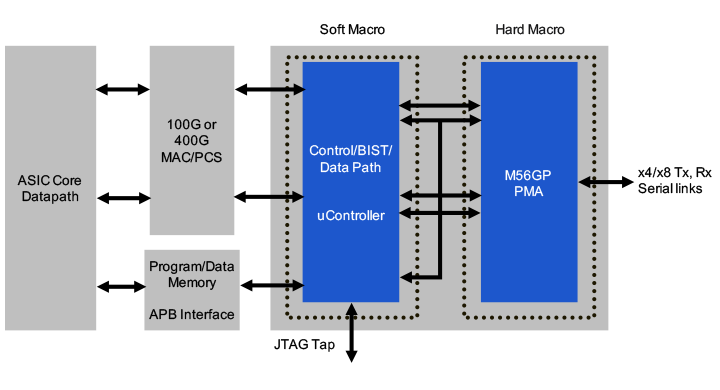

56G MPS PHY 子系统示例

56G MPS PHY 采用面向系统的方法进行设计,优化性能和功能时考虑了接口、互连和信道,以最大限度地提高在当今最具挑战性的系统环境和应用中的灵活性。这使得该 PHY 成为多种长距离、铜缆和背板系统环境的理想选择。

可用于高级 FINFET 工艺。

解决方案产品

特点

可交付成果

服务

特点

- 支持多达 8 个双工通道和 9.95 – 56 Gbps 的数据速率

- 嵌入式微处理器可进行受固件控制的 PMA 配置、初始化和适配,从而尽量提高灵活性,减少 ASIC 集成工作量

- 带有片上电容器的 RX 前端同时支持交流耦合和直流耦合信道

- 可配置架构最大限度地降低中低损耗信道的功耗

- 灵活的 ASIC 接口,可在多个 PMA 之间共享阻抗代码,并减少片上阻抗校准所需外接参考电阻器的数量

- 可编程 TX/RX 均衡器,包括以下功能:

- 可扩展信道范围的 4 抽头发送 FFE(2 抽头前光标抽头、主抽头和 1 后光标抽头)

- 将模拟前端的 12dB 峰值增益与 CTLE 相结合

- 多抽头数字 FFE 和 DFE

- 集中式 LC-PLL 支持多种参考时钟频率和通道工作频率

- 选择性地从专用引脚或内部 ASIC 接口引脚获取差分参考时钟输入

- 所有 PMA 功能均可直接控制寄存器

- 垂直多边形方向支持沿各个 ASIC 边缘放置

- PMA 可以在广泛的工作结温范围(-20 至 105°C)内符合规范。PLL、偏置电路和数据路径可在 -40 至 125°C 正常运行

- 现场实时监控和接收数据眼电压直方图

- 内置 PRBS 生成器和检查器,并可生成自定义模式

- 数字逻辑支持 ATPG 多路扫描

- 适用于串行链路引脚的 IEEE 1149.6 JTAG 边界扫描

- 内置 BER 监控器,包括一个计算收到的总位数的 40 位计数器和一个计算模式检查器检测到的错误总数的 30 位计数器

- 支持内部串行环回和并行环回

- 可使用接口或简单的并行读写端口连接 JTAG TAP 控制器

- 模拟和数字测试总线

可交付成果

- PMA 硬核

- Verilog 模型

- LEF 摘要(.lef)

- 时序模型(.lib)

- CDL 网表(.cdl)

- ATPG 模型

- IBIS-AMI 模型

- GDSII 布局

- DRC 和 LVS 报告

- 数据表

- SoC 集成指南

- 可选设计集成和启动支持服务

服务

全面的芯片和系统设计审查

- 启动/项目审查

- 平面图审查

- 测试/符合标准的测试计划审查

- 封装设计审查

- 电路板设计审查

- 最终芯片集成审查

- 启动和测试审查

工程设计服务:

- 封装设计

- 系统板布局

- 基于统计的信号与电源完整性分析

协议兼容性

| 协议 | 数据速率 (Gbps) | 应用 |

|---|---|---|

| 400GAUI-8 LR | 53.125 | 电信和网络 |

| 400GAUI-8 MR | 53.125 | 电信和网络 |

| 100G-KR4 LR | 25.78125 | 电信和网络 |

| 10G-KR | 10.3125 | 电信和网络 |

| CEI56G-LR | 36 – 58 | 铜背板网络 |

| CEI56G-MR | 36 – 58 | 芯片间连接 |

| CEI28G-MR | 19.9 – 28.1 | 铜背板网络 |

| CEI25G-LR | 19.9 – 25.8 | 铜背板网络 |

| CEI11G-LR | 9.95 – 11.2 | 铜背板网络 |

SerDes 在 28Gbps 及更高速率下面临信号完整性挑战

随着数据速率超过 28Gbps 达到 56Gbps 甚至更高,越来越难以保持信号完整性。在高达 28Gbps 的速率下,由 1 和 0 组成的 NRZ 是首选的标准化编码方案。NRZ 有两个幅度电平,其中在每个符号中包含 1 比特信息,因此也被称为 PAM2(2 电平脉冲幅度调制)。随着串行数据速率达到每个信道 56 Gb/s,带宽增加所导致的信号损伤促使高速串行数据行业采用 PAM4,即 4 电平脉冲幅度调制。对于 PAM4 信号,波特率等于比特率的一半,奈奎斯特频率等于比特率的四分之一。与 PAM2/NRZ 相比,PAM4 通过在每个符号中传输两比特,将给定数据速率的带宽减半。工程师因此可以将信道中的比特率翻倍,而无需将所需带宽增加一倍。

发明

来自博客

资源

新闻

相关文章

视频

![Read PCI Express 5 vs. 4: What’s New? [Everything You Need to Know]](https://www.rambus.com/wp-content/uploads/2020/01/PCI-express-5-Blog-Primer-resource-library.jpg)