HBM2E 工作原理

HBM 是一款高性能内存,特点是功耗低、尺寸小。它以更低的时钟速度(与 GDDR6 相比)将 2.5D 封装与更宽的接口相结合,从而以更高的带宽功耗比效率为高性能计算应用提供更高的总吞吐量。

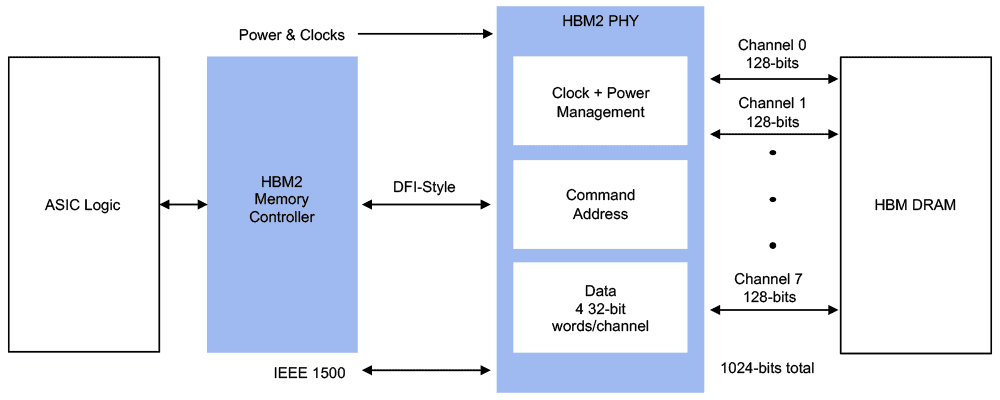

Rambus HBM2/2E PHY 完全符合 JEDEC JESD235B 标准,支持每个数据引脚高达 3.6 Gbps 的数据速率,总带宽因此达到 461 GB/s。该接口具有 8 个独立信道,每个信道包含 128 位,总数据宽度为 1024 位,支持 2、4、8 或 12 个 DRAM 的堆栈高度。此外,PHY 专为 2.5D 系统设计,配有在 3D DRAM 和 PHY 之间路由信号的内插器。这种信号密度和堆叠式外形的结合需要考虑特殊的设计。为了在这种复杂的系统中便于实现并提高设计的灵活性,Rambus 对整个 2.5D 系统进行完整的信号与电源完整性分析,以确保满足所有信号、功耗和散热要求。

Northwest Logic HBM2E控制器支持HBM2和HBM2E设备,每个数据引脚的数据速率高达3.6 Gbps。它支持所有标准通道密度,包括4、6、8、12、16和24 Gb。控制器通过Look-Ahead命令处理最大化内存带宽并使延迟最小化。核心是DFI兼容的(为HBM2E添加了扩展),并支持AXI、OCP或本地用户逻辑接口。与Rambus HBM2E PHY一起,它包括一个完全集成的HBM2E接口子系统。

AI和HPC的2.5D/3D封装解决方案

对于AI和HPC的应用,2.5D/3D结构使HBM2E存储器能够在非常紧凑的空间里提供出色的带宽、容量和延迟。然而,相同的结构也导致更大的设计复杂性,并提出了一系列新的实现注意事项。解决方案产品

- 灵活交付 IP 核:符合 ASIC/SoC 布局要求

- 速度箱:0.5 Gbps、1.0 Gbps、1.5 Gbps、1.6 Gbps、1.8 Gbps、2.0 Gbps、2.4 Gbps、3.0 Gbps、 3.2 Gbps、3.6 Gbps

- 8 个信道和 16 个伪信道

- 支持 DRAM 2、4 或 8 堆栈

- DFI 3.1 式接口,易于与内存控制器集成

- 内存控制器或 PHY 可以是 ASIC 接口主机(PHY 独立模式)

- 可选择低功耗运行状态

- 可编程输出阻抗

- 用于通道维修的引脚可编程支持

- 输出阻抗的 ZQ 校准

- IEEE 1500 测试支持

- 自动测试支持

- SSO 降噪

- 与 DRAM 间距相匹配的微凸点间距

- 采用 13 层金属堆栈

- 东西方向(PHY 可以放置在芯片角)

- 状态观察寄存器接口

- LabStation™ 软件环境,适于进行系统级启动、符合标准的测试和验证

- 经过全面符合标准测试的硬核 (GDSII)

- 完整的设计视图:

- 门级模型和 IO 模型

- 验证测试平台

- 布局摘要(.lef)

- 时序模型(.lib)

- 完整文件:

- 数据表

- 封装和内插器设计指南

- ASIC/DFT 制造指南

- 测试和符合标准的测试用户指南

- Verilog 模型

- CDL 网表(.cdl)

- GDSII 布局

- DRC 和 LVS 报告

全面的芯片和系统设计审查

- 启动/项目审查

- 平面图审查

- 测试/符合标准的测试计划审查

- 封装设计审查

- 电路板设计审查

- 最终芯片集成审查

- 启动和测试审查

工程设计服务:

- 封装设计

- 系统板布局

- 基于统计的信号与电源完整性分析

协议兼容性

| 协议 | 数据速率 (Gbps) | 应用 |

|---|---|---|

| HBM2E | 0.5-3.6 | 数据中心和网络 |

| HBM2 | 0.5-2 | 数据中心和网络 |

Memory Systems for AI and Leading-Edge Applications

Thanks to rapid advancements in computing, neural networks are fueling tremendous growth in AI for a broad spectrum of applications. Learn about the memory architectures, and their relative advantages, at the heart of the AI revolution.

发明

来自博客

资源

新闻

相关文章