LabStation 平台工作原理

随着各新工艺节点的出现、性能的提升和新 IP 块的增加,高级 SoC 的设计也随之变得更加复杂。设计人员在验证和确认芯片功能方面正面临越来越多的挑战。

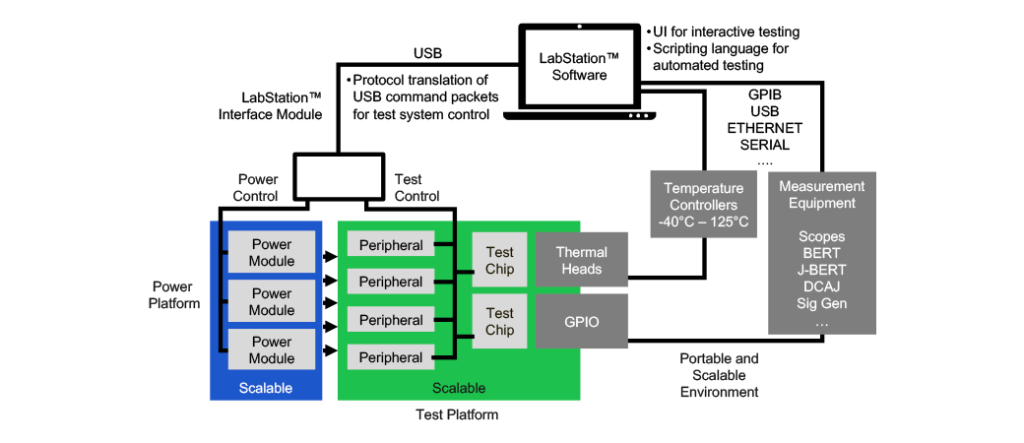

LabStation 验证平台是一款全面的工具套件,用于快速启动、验证和符合标准的测试复杂的低功耗、高性能内存和串行链路 IP。该平台旨在便于使用,提高生产效率,同时提高测试结果的准确性,增强对系统性能的信心。

该平台增强了用户界面,以改善 IP 的可用性与控制,包括对片上电路、板载设备、测量设备和第三方工具的访问。这有助于客户验证我们的 R+ 内存和串行链路 PHY,以提高芯片和系统的质量并缩短上市时间。该套件已经过大容量应用验证,并提供了一套有效的片上自动化测试工具,可以验证高级内存子系统和高速串行链路的设计,以便投产。

我们的 LabStation 平台提供了一个全自动的符合标准的测试环境。这简化了符合标准的测试过程,并通过自动化测试脚本,在各种温度和电压条件下快速准确地收集非常高的吞吐量数据,缩短了上市时间。

最后,LabStation 工具套件支持对使用 2.5 和 3D 封装的芯片执行高级测试功能,在这种情况下,用手动探针进行测量并不准确,在某些情况下不可能做到。

AI和HPC的2.5D/3D封装解决方案

对于AI和HPC的应用,2.5D/3D结构使HBM2E存储器能够在非常紧凑的空间里提供出色的带宽、容量和延迟。然而,相同的结构也导致更大的设计复杂性,并提出了一系列新的实现注意事项。解决方案产品

特点

可交付成果

特点

- 测量目标 BER(误码率)的电压和时序裕度眼图

- 提供片上基础架构,自动测量电源噪声、配电网阻抗和信道阶跃响应

- 在高数据速率下,片上测量的结果比封装外测量更精确

- 支持 2.5/3D 集成和小型封装测试

- 高精度功耗测量

- 用户界面改进了对组件目录、寄存器详细值以及命令缓冲器和操作日志的访问

可交付成果

- 全面的芯片和系统设计审查

- 优化了用户界面的 LabStation 专有软件

- LabStation 接口模块 (LIM)

- 系统测试板

- 测试芯片

- 配电板

发明

FlexPhase™ 时序调整电路

FlexPhase 每比特时序调整电路校正数据和时钟信号的偏差,从而提高信号完整性并简化封装和 PCB 系统设计。

输出驱动器校准

输出驱动器校准功能使 SoC 设计人员可以将输出信号调整到最佳水平,以提高数据速率和系统电压裕度。

来自博客

资源

新闻

相关文章

视频