新闻摘要:

- 第二代寄存时钟驱动器(RCD)将DDR5数据速率提高17%,同时降低延时和功耗

- 为服务器主存储器提供5600MT/s DDR5 RDIMM的关键支持

- 展现了Rambus在下一代服务器DDR5内存接口芯片领域的持续领先地位

北京2021年11月17日 /美通社/ — 作为业界领先的芯片和IP核供应商,致力于使数据传输更快更安全,Rambus Inc.(纳斯达克股票代码:RMBS)今日宣布已开始向主要的DDR5内存模块(RDIMM)供应商提供数据传输速率可达5600MT/s的第二代RCD芯片样品。第二代RCD芯片性能更强,较第一代4800MT/s的Rambus DDR5 RCD的数据传输速率提高了17%。通过关键创新,Rambus能够以更低的延迟和能耗提供5600 MT/s的性能,同时优化定时参数,提升RDIMM的裕量。

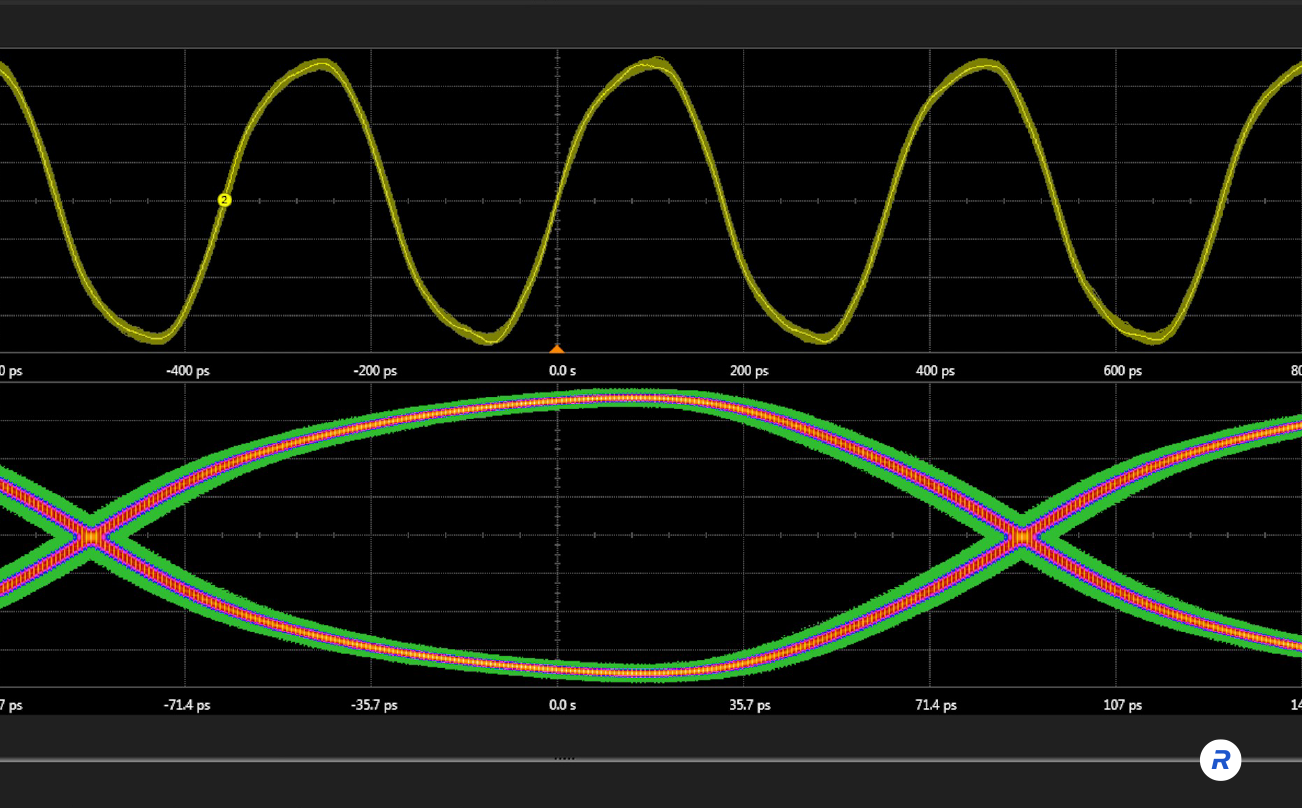

Rambus 5600 MT/s DDR5 RCD眼图

IDC计算半导体研究部门副总裁Shane Rau表示:“高阶工作负载正在持续推动对更大内存带宽的需求。以Rambus为代表的DDR5生态系统参与者必须不断提高性能标准,以满足数据中心应用迅速增长的需求。”

Rambus首席运营官范贤志(Sean Fan)表示:“RCD是DDR5服务器DIMM的关键赋能部件,提供了下一代数据中心所需的带宽和容量。实现5600MT/s的数据传输速率是Rambus在DDR5内存接口产品领域保持领先的最新力证。”

与DDR4相比,DDR5内存在DIMM中内置更多智能功能,可将数据传输速率提高一倍,容量提升至四倍,同时还降低了功耗、提高了内存效率。Rambus内存接口芯片是下一代服务器实现全新性能水平的关键。

如需了解Rambus DDR5 RCD的更多详细信息,请访问我们的网站。