HBM3是一款高性能内存,能够以更低的功耗和更紧凑的空间提供卓越的带宽。它利用3D内存和2.5D架构以及宽接口,以每瓦特高带宽能效为AI/ML和HPC应用提供高吞吐量。Rambus HBM3内存子系统支持每数据引脚高达8.4 Gbps的数据速率。子系统具有16个独立信道,每个信道包含64位,总数据带宽为1024位。堆栈由2、4、8、12或16个DRAM组成,每个堆栈由此产生的带宽为1075.2 GB/s。Rambus HBM3内存子系统由HBM3 PHY和控制器组成,实现了性能最大化且易于与SoC集成。

HBM3内存:向更高带宽突破

AI/ML对更高带宽永无止境的需求,推动着计算机软硬件各方面的迅速改进。HBM内存作为一种理想的解决方案,能够充分满足AI/ML训练对高带宽的要求。由于其特殊的2.5D架构,使得我们在设计上需要加入更多的考量。如今,我们迎来了新一代的HBM,它的出现将内存和容量提高至新的高度。设计人员可以通过Rambus HBM3-Ready内存子系统解决方案实现更高的性能水平。

从数据中心到终端设备:使用GDDR6进行AI/ML推理

GDDR的诞生起初是为了支持主机和PC上的3D游戏。其卓越的性能如今使其成为AI/ML推理的理想解决方案。随着推理从数据中心的核心转移到网络边缘,并最终转移到更为广泛的由AI驱动的物联网设备,GDDR内存的高带宽、低延迟、低功耗和对大容量应用的适用性正变得越来越重要。该标准的最新版本GDDR6内存将数据速率提高至18 Gbps,设备带宽提高至72 Gbps。

MACsec 基本原理:保护动态数据安全

对于端到端的数据安全性,必须确保数据在静态(在设备中处理和存储的数据)和动态(在互联设备间通信的数据)时均得到安全保护。对于静态数据,植根于芯片中的硬件信任根(Hardware Root of Trust) 能为所有设备的安全性奠定基础。同样地,植根于基础通信层(第二层)的硬件中的MACsec,能够为整个以太网网络中移动的数据提供信任基础。

CXL内存互联计划:引领数据中心架构进入新时代

为了应对数据呈指数级增长趋势所带来的挑战,整个行业即将迎来数据中心架构的突破性转变,这将从根本上改变全球数据中心的性能、效率和成本。近几十年来未有重大变化的服务器架构,如今正在其设计上迈出革命性的一步,以满足高级工作负载带来的日益增长的数据及性能的需求。

Rambus发布业界首款5600 MT/s DDR5寄存时钟驱动器(RCD)

新闻摘要:

- 第二代寄存时钟驱动器(RCD)将DDR5数据速率提高17%,同时降低延时和功耗

- 为服务器主存储器提供5600MT/s DDR5 RDIMM的关键支持

- 展现了Rambus在下一代服务器DDR5内存接口芯片领域的持续领先地位

北京2021年11月17日 /美通社/ — 作为业界领先的芯片和IP核供应商,致力于使数据传输更快更安全,Rambus Inc.(纳斯达克股票代码:RMBS)今日宣布已开始向主要的DDR5内存模块(RDIMM)供应商提供数据传输速率可达5600MT/s的第二代RCD芯片样品。第二代RCD芯片性能更强,较第一代4800MT/s的Rambus DDR5 RCD的数据传输速率提高了17%。通过关键创新,Rambus能够以更低的延迟和能耗提供5600 MT/s的性能,同时优化定时参数,提升RDIMM的裕量。

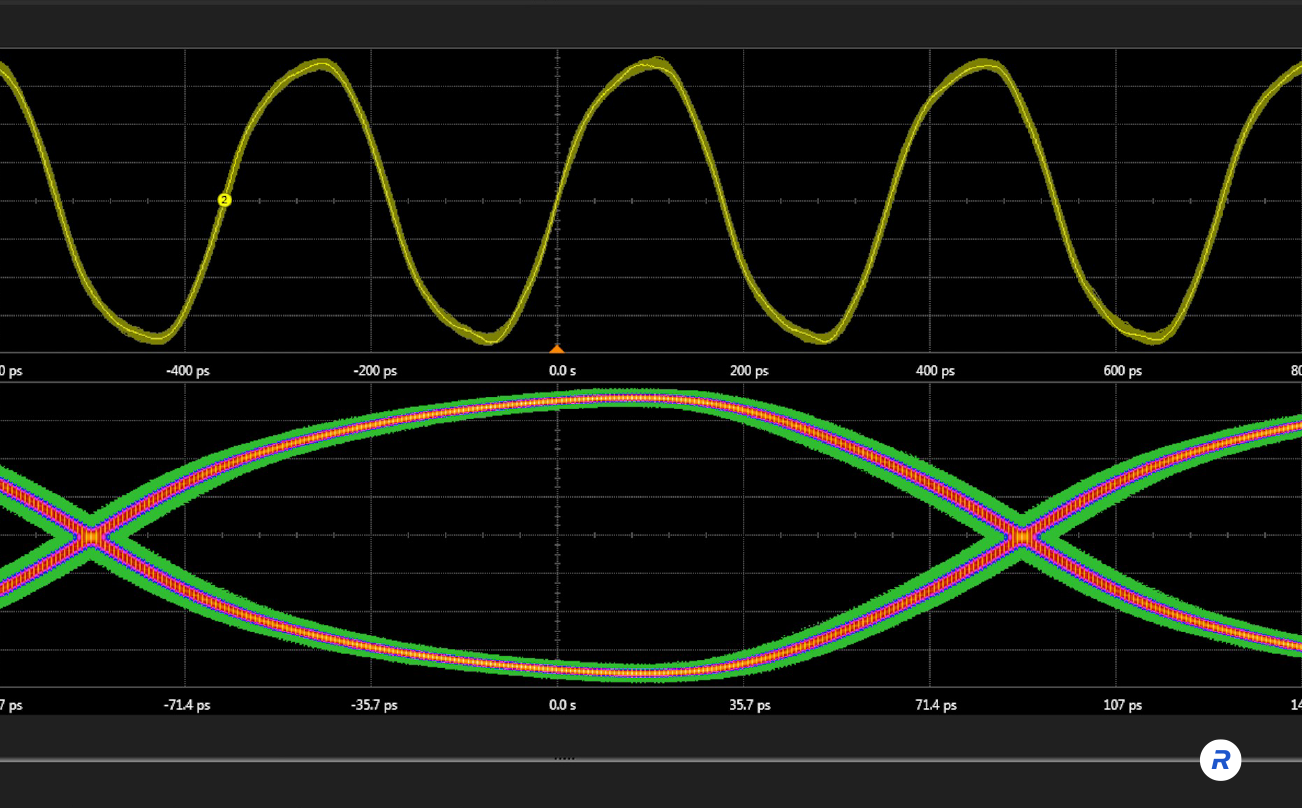

Rambus 5600 MT/s DDR5 RCD眼图

IDC计算半导体研究部门副总裁Shane Rau表示:“高阶工作负载正在持续推动对更大内存带宽的需求。以Rambus为代表的DDR5生态系统参与者必须不断提高性能标准,以满足数据中心应用迅速增长的需求。”

Rambus首席运营官范贤志(Sean Fan)表示:“RCD是DDR5服务器DIMM的关键赋能部件,提供了下一代数据中心所需的带宽和容量。实现5600MT/s的数据传输速率是Rambus在DDR5内存接口产品领域保持领先的最新力证。”

与DDR4相比,DDR5内存在DIMM中内置更多智能功能,可将数据传输速率提高一倍,容量提升至四倍,同时还降低了功耗、提高了内存效率。Rambus内存接口芯片是下一代服务器实现全新性能水平的关键。

如需了解Rambus DDR5 RCD的更多详细信息,请访问我们的网站。