PCIe 6.0 提供了许多令人兴奋的新功能,包括 64 GT/s 数据速率、PAM4 信令、前向纠错和低功耗 L0p 模式。 在本次演讲中,Larry Lai 将带您了解,在开始 PCIe 6.0 设计之前需要了解的所有系统设计考量,包括如何充分利用每个 PCIe 设备。

使用 GDDR6 内存为 AI/ML 推理提供动力

GDDR6 内存提供了令人印象深刻的带宽、容量、延迟和功耗组合。Larry Lai 将讨论这些功能如何使其成为边缘中 AI/ML 推理的理想内存选择,并重点介绍当以超高数据速率实施GDDR6内存时需要牢记的一些关键设计考量。

Rambus 通过业界首款第四代 DDR5 RCD 提升数据中心服务器性能

新闻摘要:

- 数据速率提高到 7200 MT/秒,内存带宽比目前的第一代 DDR5 设备提高了 50%

- 扩大在服务器主内存中关键内存接口芯片解决方案领域的领先地位

- 支持针对生成式人工智能和其他高级数据中心工作负载的服务器性能加速路线图

中国北京,2023年12月27日 —— 作为业界领先的芯片和半导体IP供应商,致力于使数据传输更快更安全,Rambus Inc.(纳斯达克股票代码:RMBS)今日宣布推出最先进的第四代 DDR5 寄存时钟驱动器 (RCD),并于 2023 年第四季度开始向主要 DDR5 内存模块 (RDIMM) 制造商提供样品。Rambus 第四代 RCD 将数据传输速率提高到 7200 MT/s,设立了新的性能标杆,相比目前的 4800 MT/s DDR5 模块解决方案,其内存带宽提高了 50%。它支持服务器主内存性能的快速提升,以满足生成式人工智能和其他高级数据中心工作负载的需求。

Rambus首席运营官范贤志表示:“内存是服务器性能的重要推动因素,在生成式人工智能等高要求工作负载的推动下,对更大内存带宽的需求继续急剧上升。Rambus 第四代 DDR5 RCD 是我们致力于提供领先于市场需求的产品,以支持客户当前和计划中的服务器平台的最新证明。”

IDC计算半导体的副总裁Shane Rau表示:“在人工智能领域令人惊叹的创新步伐引导下,高级工作负载正推动数据中心新服务器平台的加速发展,DDR5 RCD 对于支持人工智能服务器中 RDIMM 所需的性能、功耗和信号完整性至关重要。”

Rambus DDR5内存接口芯片组包含RCD、串行检测(SPD)集线器和温度传感器,对于提升领先服务器的性能水平十分重要。凭借在高性能内存领域积累30多年的经验,Rambus以其信号完整性(SI)/电源完整性(PI)方面的专业技术著称。这些专业技术有助于实现 DDR5 内存接口芯片,为数据中心服务器 RDIMM 提供卓越的性能和可靠性。

产品上市时间

Rambus 7200 MT/s DDR5 RCD 于今日上市。

更多信息:

如需了解更多关于Rambus DDR5内存接口芯片的信息,敬请访问: rambus.com/partners/rambus-partner-program/。

Rambus通过9.6 Gbps HBM3内存控制器IP大幅提升AI性能

新闻摘要:

• 为增强AI/ML及其他高级数据中心工作负载打造的 Rambus 高性能内存 IP产品组合

• 高达9.6 Gbps的数据速率,支持HBM3内存标准的未来演进

• 实现业界领先的1.2 TB/s以上内存吞吐量

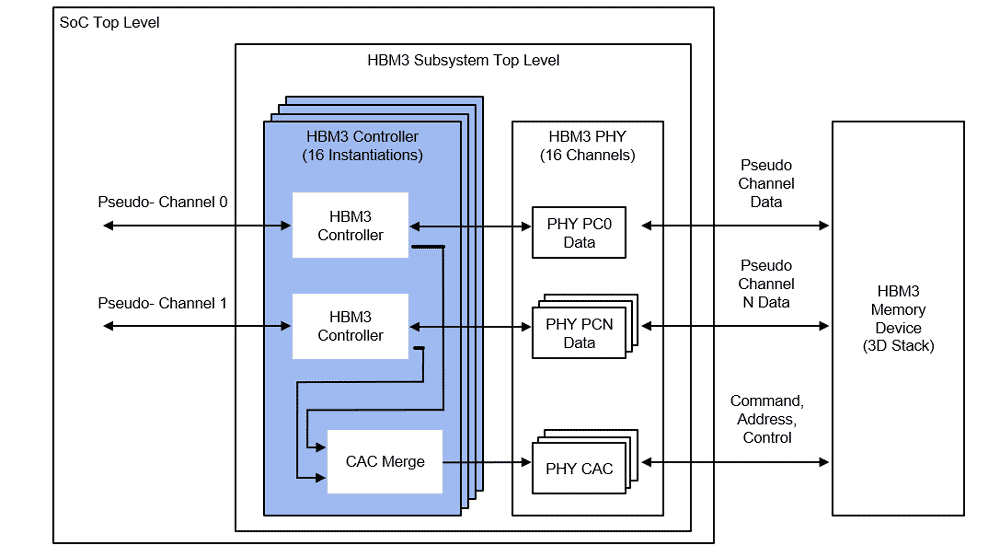

中国北京,2023年12月 7日– 作为业界领先的芯片和IP核供应商,致力于使数据传输更快更安全,Rambus Inc.(纳斯达克股票代码:RMBS)今日宣布Rambus HBM3内存控制器IP现在可提供高达9.6 Gbps的性能,可支持HBM3标准的持续演进。相比HBM3 Gen1 6.4 Gbps 的数据速率,Rambus HBM3内存控制器的数据速率提高了50%,总内存吞吐量超过1.2 TB/s,适用于推荐系统的训练、生成式AI以及其他要求苛刻的数据中心工作负载。

Rambus IP核部门总经理 Neeraj Paliwal 表示:“大语言模型要求高性能内存技术的不断进步,使得HBM3成为AI/ML训练的首选内存。依靠Rambus的创新和卓越的工程技术,我们的HBM3内存控制器IP可提供业界领先的9.6 Gbps性能。”

IDC内存半导体副总裁 Soo-Kyoum Kim 表示:“HBM 是更快速且更高效的处理大型 AI 训练和推理集的关键内存技术,比如用于生成式 AI 的训练和推理。对于像Rambus这样的 HBM IP供应商来说,持续提高性能来支持满足市场苛刻要求的领先 AI 加速器的意义重大。”

HBM采用创新的2.5D/3D架构,为AI加速器提供具有高内存带宽和低功耗的解决方案。凭借极低的延迟和紧凑的封装,HBM已成为AI训练硬件的首选。

Rambus HBM3 内存控制器 IP 专为需要高内存吞吐量、低延迟和完全可编程性应用而设计。该控制器是一种高度可配置的模块化解决方案,可根据每个客户对尺寸和性能的独特要求进行定制。对于选择第三方HBM3 PHY的客户,Rambus还提供HBM3控制器的集成与验证服务。

产品及更多信息:

Rambus HBM3内存控制器从即日起提供许可证。如需了解更多信息,请访问www.rambus.com/interface-ip/hbm/

利用 VESA 视频压缩和 MIPI DSI-2 实现高性能显示

视觉无损视频压缩对于满足不断增长的具有更高分辨率、更快刷新率和更大像素深度的尖端显示的带宽要求是至关重要的。 本次演讲将向设计人员讲解,在不影响显示质量、电池寿命或成本等条件下,如何结合使用 VESA 视频压缩和 MIPI DSI-2 技术来开发尖端显示产品。

用于 PUF 的加密辅助数据映像的防篡改优势

PUF 是一种混合信号电路,其依靠特定芯片特有的变化来自生成数字“指纹”。大多数 PUF 需要在初始数字化过程中生成“辅助数据”映像,也被称为注册。 利用 PUF 和加密辅助数据的芯片唯一的转换功能,可实现不可克隆的质询-响应机制,将正版芯片与完美的克隆芯片区分开来。