Memory Interface Chips

Providing memory bandwidth and capacity to unleash the power of multicore processors

Home > Memory Interface Chips

Tackling advanced workloads requires ever increasing levels of memory bandwidth and capacity. With over three decades of high-performance memory expertise, Rambus delivers the most advanced memory interface chipset solutions.

For data center applications, the Rambus Memory Interface Chip portfolio includes DDR5 RDIMM and MRDIMM chipsets for the latest generation DDR5-based servers as well as those slated for release in the years ahead. For LPDDR5X-based memory in server systems, Rambus offers an industry-leading SOCAMM2 chipset.

As advanced technologies honed in the data center proliferate to the client space, the Rambus DDR5 Client DIMM Chipset enables client DIMMs (CSODIMMs and CUDIMMs) to deliver new levels of memory performance for PC desktops and laptops. The Rambus LPCAMM2 Client Chipset enables state-of-the-art memory performance in ultra-thin notebook PCs.

The Rambus DDR5 Server DIMM chipset includes the DDR5 Registering Clock Drivers (RCD), Power Management ICs (PMICs), Serial Presence Detect Hubs (SPD Hub) and Temperature Sensors (TS) for DDR5 RDIMMs. For Multiplexed Rank DIMMs (MRDIMMs), Rambus offers DDR5 Multiplexed Registering Clock Drivers (MRCD) and Multiplexed Data Buffers (MDB) as well as PMIC, SPD Hub and TS chips. These market-leading solutions deliver performance of up to 8000 MT/s (RDIMM) and 12800 MT/s (MRDIMM) supporting current and future data center servers.

The Rambus DDR4 Server DIMM chipset includes the DDR4 Registering Clock Driver (RCD) and Data Buffer (DB). These solutions deliver performance levels up to 3200 MT/s for current DDR4 RDIMMs.

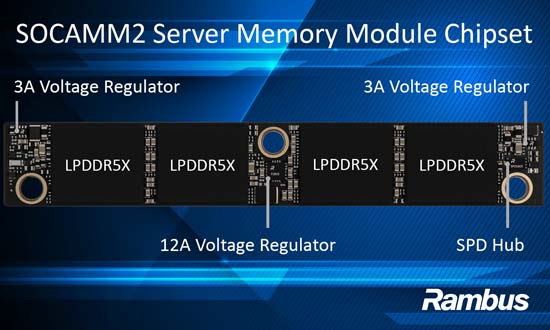

The Rambus SOCAMM2 Server Chipset includes 12 Amp and 3 Amp Voltage Regulators (VR) and Serial Presence Detect Hubs (SPD Hub). This industry-leading chipset solution supports performance up to 9600 MT/s in a server-class LPDDR-based compression-attached memory module.

The Rambus DDR5 Client DIMM Chipset includes the DDR5 Client Clock Driver (CKD) and Serial Presence Detect Hubs (SPD Hub). These solutions enable state-of-the-art data rates of up to 7200 MT/s to deliver breakthrough performance in next-generation AI PCs.

The Rambus LPCAMM2 Client Chipset includes Power Management IC (PMIC) and Serial Presence Detect Hub (SPD Hub). This chipset solution enables the revolutionary LPCAMM2 form factor, which brings the bandwidth and capacity benefits of LPDDR5 memory to PCs with the flexibility and reliability benefits of a module.

DDR5 Memory Enables Next-Generation Servers

An exponential rise in data volume, and the rapid increase of advanced workloads like AI/ML training, requires constant innovation in all aspects of computing. Yet given the broad infrastructure implications, main memory technology changes infrequently, once every 6 or 7 years. The transition to DDR5 is a watershed industry event as it will be the main memory solution in servers for the rest of this decade.