Forward Error Correction (FEC) IP Cores

Home > Interface IP > Forward Error Correction (FEC) IP Cores

DisplayPort and HDMI Forward Error Correction IP

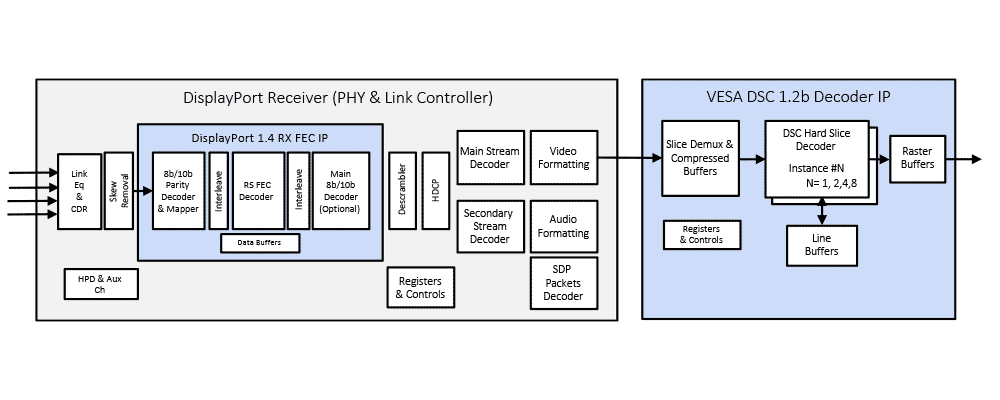

Rambus DisplayPort™ 1.4 and HDMI® 2.1 FEC IP cores deliver a glitch-free visual experience for end users, while enabling designers to use VESA® Display Stream Compression (DSC) to reach higher resolutions and refresh rates.

DisplayPort 1.4 and HDMI 2.1 FEC IP

| Feature | DisplayPort 1.4 | HDMI 2.1 |

|---|---|---|

| Reed Solomon (RS) FEC | RS (254,250) 10-bit symbols | RS (255,251) 8-bit symbols |

| Lane Operation | 1, 2 and 4-lane modes NB: 4-lane mode requires 2 FEC IP core instances | 3-lane and 4-lane modes |

| Statistics Interface | Included in Rx | Included in Rx |

| DP Main 8b/10b Encoder | Tx: Included Rx: Optional |

Using Forward Error Correction with VESA DSC Compression

Bit errors on an uncompressed video stream have no visual impact. However, bit errors on a compressed video stream result in an impaired visual experience for a user. For this reason, DisplayPort 1.4 and HDMI 2.1 mandate the use of Reed Solomon (RS) FEC when enabling VESA DSC.

For example, DisplayPort 1.4 has a bit error rate (BER) of 10-9 without FEC. The BER is the probability that a given bit will be corrupted. With the use of FEC, the BER is lowered to 10–18. At full DisplayPort bandwidth (32.4Gbps), this represents approximately one uncorrected error per year.

DisplayPort 1.4 FEC Tx and Rx

- VESA DisplayPort 1.4 compliant

- Reed-Solomon RS (254,250) FEC, 10-bit symbols

- Two-way interleaving for 1-, 2- and 4-lane modes (4-lane mode requires 2 FEC IP core instances)

- DisplayPort main 8b/10b encoder included (Tx only)

- Status and control can be done with signals or optionally via an integrated APB register module (Rx)

- Single unified APB interface supports 4-lane mode (Rx)

- Performance monitoring and statistics counters (Rx)

HDMI 2.1 FEC Tx and Rx

- HDMI 2.1 compliant

- Reed-Solomon RS (255,251) FEC, 8-bit symbols

- Supports 3-lane and 4-lane operation

- Error counters included (Rx only)

- Verilog RTL

- Complete documentation

- Expert technical support

- Maintenance updates

- Engineering design services

- Customization

- SoC integration