最后更新于:2021 年 1 月 18 日 7 月 14 日, JEDEC发布 JESD79-5 DDR5 SDRAM 标准,这标志着行业即将向 DDR5 服务器双列直插式内存模块 (DIMM) 过渡。DDR5 内存带来了一系列关键的性能和功率方面的改进,同时也引入了新的设计挑战。服务器系统架构师、设计师和消费者想要了解,相较于 DDR4,DDR5 有什么新改变,以及应如何更好地应用这款新内存。

本文将解答:

DDR5 与 DDR4 相比有什么区别?

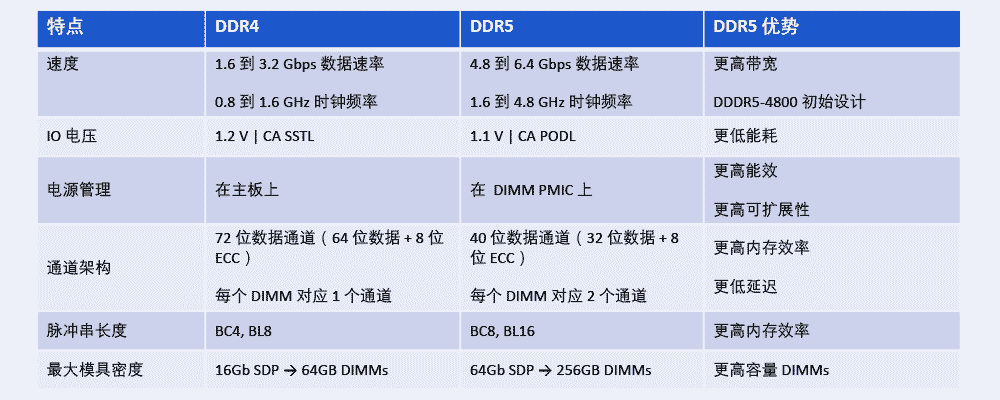

下表 1 显示了从 DDR4 向 DDR5 DIMM 过渡的过程中,六项主要规格的改进。

表 1。DDR5 与 DDR4:DDR5 对比 DDR4 DIMM 的优势

1. DDR5 数据速率提升至 8.4Gbps

人们对内存带宽的需求永不满足,而 DDR5 有助于满足这种对速率的无尽需求。在 1.6 GHz 时钟频率下,DDR4 DIMM 的传输带宽最高可达 3.2 Gbps,而初代 DDR5 即能够将这个数字提升 50%,即 4.8Gbps。DDR5 内存数据速率最终将达到 8.4Gbps。DDR5 中还纳入了判断反馈均衡器 (DFE) 等新功能以实现更高的 IO 速度和数据速率。

2. 电压更低代表功耗更低

第二个主要改变是降低了工作电压 (VDD),这有助于降低功耗。使用 DDR5,DRAM、缓冲芯片寄存时钟驱动器 (RCD) 和数据缓冲器 (DB) 的电压可从 1.2V 降至 1.1V。Command / Address (CA)信号由SSTL改变至PODL, 当引脚停留再高阻状态时,具有无静电燃烧的优点。

3. 3. DDR5 新电源架构

第三个也是最主要的改变是电源架构。在 DDR5 DIMM 中,电源管理由主板转移至 DIMM 本身。 DDR5 DIMM 在 DIMM 上将具有 12V 电源管理 IC (PMIC),以实现更好的系统电源负载颗粒度。PMIC 分配 1.1 V VDD 电源,通过对电源进行更好的 on-DIMM 控制来帮助实现信号完整性和噪声控制。

4. DDR5 与 DDR4:通道架构

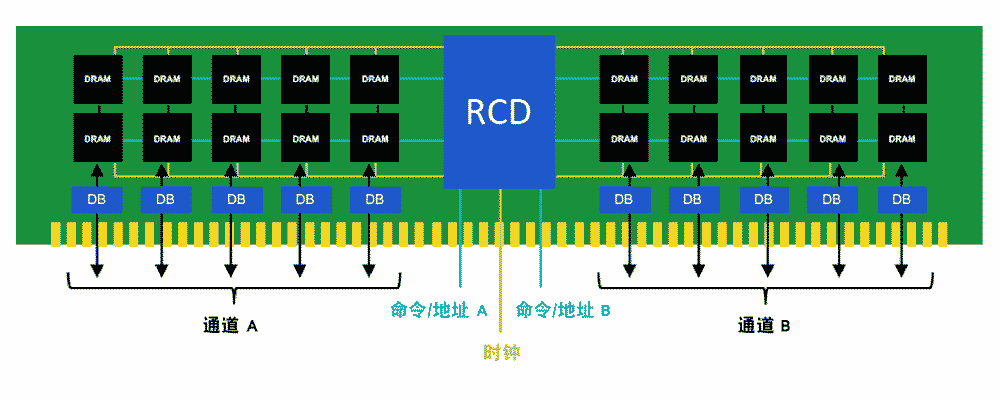

DDR5 的另一个重大变化是采用了新的 DIMM 通道架构,这项变化在我们的榜单上排名第四。DDR4 DIMM 具备 72 位总线,其中包含 64 个数据位和 8 个 ECC 位。采用 DDR5时,每个 DIMM 均具备两个通道。每个通道均为 40 位宽:即 32 个数据位和 8 个 ECC 位。在数据宽度相同(共 64 位)的条件下,拥有两个较小的独立通道可提升内存访问效率。因此,应用者不仅可以受益于 DDR5 带来的速率提升,且更高的 MT/s 的优势也可以因更高的效率而放大。

在 DDR5 DIMM 的架构中,DIMM 左右侧分别由一个独立的 40 位宽通道提供服务,它们共享 RCD。在 DDR4 中,RCD 每侧提供两个输出时钟。而在 DDR5 中,RCD 每侧提供四个输出时钟。在具有 x4 DRAM 的最高密度 DIMM 中,这允许每组 5 个 DRAM(单等级,半通道)接收自己的独立时钟。为每个通道提供独立的时钟可改善信号完整性,从而有助于解决由于降低 VDD 而产生的噪声容限较低的问题(来自上述更改 2)。

5. 更长的突发长度

第五项重大变化是突发长度。DDR4 的突发斩波长度为四,突发长度为八。DDR5 的突发斩波和突发长度将扩展到八和十六,以增加突发有效负载。在突发长度为十六 (BL16) 的情况下,允许单个突发访问 64 字节的数据,这是典型的 CPU 缓存行大小。仅需使用两个独立通道中的一个即可实现此操作。这显著地提升了并发性,并通过两个通道提高了内存效率。

6. DDR5 支持更高容量的 DRAM

第六个也是最后一个值得一提的改变是 DDR5 对更高容量 DRAM 设备的支持。借助 DDR5 缓冲芯片 DIMM,服务器或系统设计师可在单个管芯封装中支持多达 64 Gb DRAM 的密度。DDR4 单芯片封装 (SDP) 最大仅可容纳16 Gb DRAM。DDR5 支持片上 ECC、错误透明模式、封装后修复和读写 CRC 模式等功能,从而支持更高容量的 DRAM。更高容量的设备显然会促成更高容量的 DIMM。因此,在 DDR4 DIMM 的容量最高可达 64GB(使用 SDP)的条件下,DDR5 基于 SDP 的 DIMM 将这个数字提升至 256GB。

DDR5 的设计面临哪些挑战?

DDR5 的这些变化引入了许多设计需求,涉及更高的速度和更低的电压,这提出了新一轮的信号完整性挑战。设计师将需要确保主板和 DIMM 能够处理更高的信号速度。在执行系统级仿真时,需要检查所有 DRAM 位置的信号完整性。

DDR4 在信号完整性方面所面临的主要设计挑战在于双数据速率 DQ 总线,而对低速命令地址 (CA) 总线的关注较少。而在 DDR5 的设计中,即使是 CA 总线也会要求特别注意信号完整性。对于 DDR4,曾考虑过用差分反馈均衡 (DFE) 来改善 DQ 数据通道。而对于 DDR5,连RCD 的 CA 总线接收器也需要DFE 选项,以确保良好地接收信号。

另一个考量是主板上的供电网络 (PDN),包括带 PMIC 的 DIMM。考虑到更高的时钟和数据速率,需要确保 PDN 能够处理好高速且信号完整性良好的运行负载,并为 DIMM 提供干净良好的电源。

连接主板和 DIMM 的 DIMM 连接器也必须处理好新的时钟和数据速率。对于系统设计师而言,由于印刷电路板 (PCB) 周围的时钟速度和数据速率更高,系统设计时必须更加重视电磁干扰和电磁兼容(EMI 和 EMC)。

DDR5 内存接口芯片组如何发挥 DDR5 的 DIMM 优势?

值得庆幸的是,DDR5 内存接口芯片改善了从主机内存控制器发送到 DIMM 的命令和地址信号的信号完整性。两个通道中的每个通道的总线都通向寄存时钟驱动器,然后呈扇形散开到 DIMM 的两侧。有效地减少了主机内存控制器观测到的 CA 总线负载。

DDR5 数据缓冲芯片将减少数据总线的有效负载,从而在不牺牲延时性能的情况下,允许 DIMM 上更高容量DRAM。

Rambus 提供DDR5 内存接口芯片组,帮助设计师全方位利用 DDR5 的优势,处理因为数据、CA 和时钟速率加快而出现的信号完整性问题。

Rambus 作为知名的信号完整性 (SI) 和电源完整性 (PI) 领域领导者,在过去 30 年里持续为市场提供最高性能系统。

Explore more primers:

– 硬件信任根:您所需要了解的一切

– PCI Express 5 与 PCI Express 4:有哪些新功能?

– Compute express link: All you need to know

– HBM2e 实施与选型终极指南

发表回复