HBM3E / HBM3 Controller IP

Home > Interface IP > HBM Controller IP > HBM3E Controller

The Rambus HBM3E / HBM3 controller cores are designed for use in applications requiring high memory bandwidth and low latency including AI/ML, HPC, advanced data center workloads and graphics.

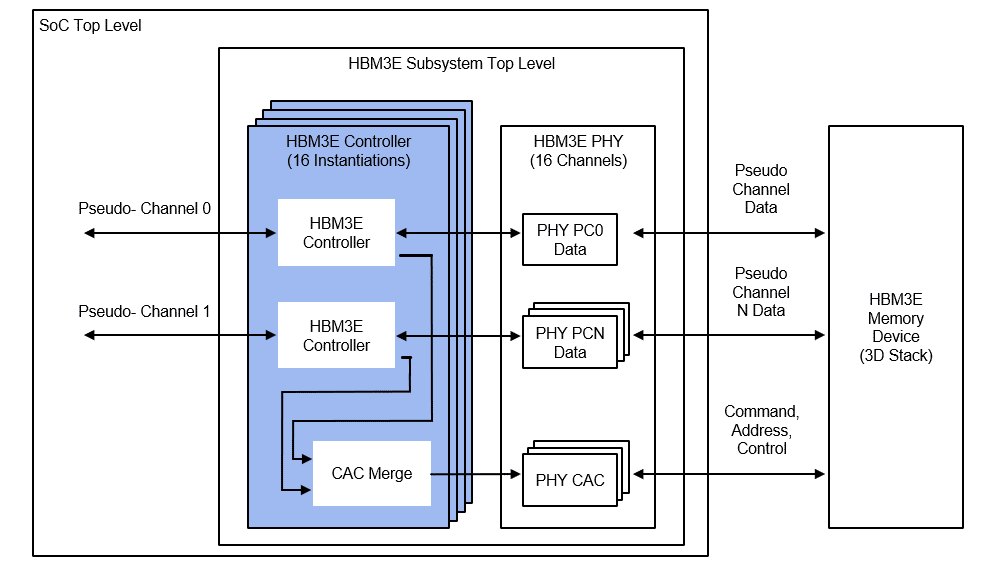

The HBM3E Memory Subsystem

HBM3E is a high-performance memory that features reduced power consumption and a small form factor. It combines a 2.5D/3D architecture with a 1024-bit wide interface operating at a lower clock speed (as compared to GDDR6) to deliver higher overall throughput at a higher bandwidth-per-watt efficiency for AI/ML and HPC applications.

The Rambus HBM3E memory controller supports data rates up to 9.6 Gbps per data pin. The interface features 16 independent channels, each containing 64 bits for a total data width of 1024 bits. At maximum data rate, this provides a total interface bandwidth of 1229 GB/s.

The Rambus HBM3E memory controller supports HBM3E memory devices with 2, 4, 8, 12 and 16 DRAM stack height with densities of up 32 Gb. The subsystem maximizes bandwidth and latency via Look-Ahead command processing.

The Rambus HBM3E memory controller combined with the customer’s choice of PHY comprises a complete HBM3E memory subsystem.

Ask the Experts: HBM3E Memory Interface IP

Solution Offerings

- Supports HBM3E / HBM3 memory devices

- Supports all standard HBM3 channel densities (up to 32 Gb)

- Supports up to 9.6 Gbps/pin (HBM3E) or 8.4 Gbps/pin (HBM3)

- Refresh Management (RFM) support

- Maximizes memory bandwidth and minimizes latency via Look-Ahead command processing

- Integrated Reorder functionality

- Achieves high clock rates with minimal routing constraints

- Self-refresh and Power-down Low Power Modes

- Support for HBM3 RAS features

- Built-in hardware-level performance Activity Monitor

- DFI compatible

- End-to-end data parity

- Supports AXI or native interface to user logic

- Core (source code)

- Testbench (source code)

- Complete documentation

- Expert technical support

- Maintenance updates

Engineering Design Services:

- Customization

- SoC Integration

HBM3E Memory: Break Through to Greater Bandwidth

Delivering unrivaled memory bandwidth in a compact, high-capacity footprint, has made HBM the memory of choice for AI training. HBM3 is the third major generation of the HBM standard, with HBM3E offering an extended data rate and the same feature set. The Rambus HBM3E/3 Controller provides industry-leading performance to 9.6 Gb/s, enabling a memory throughput of over 1.23 TB/s for training recommender systems, generative AI and other compute-intensive AI workloads.

Protocol Compatibility

| Protocol | Data Rate (Gbps) Max. | Application |

|---|---|---|

| HBM3E | 9.6 | AI/ML, HPC, Graphics |

| HBM3 | 8.4 | AI/ML, HPC, Graphics |