DDR3 Controller

Home > Interface IP > DDR Memory Controller IP > DDR3 Controller

The Rambus DDR3 controller core is designed for high memory throughput, high clock rates, and full programmability in computing and networking applications.

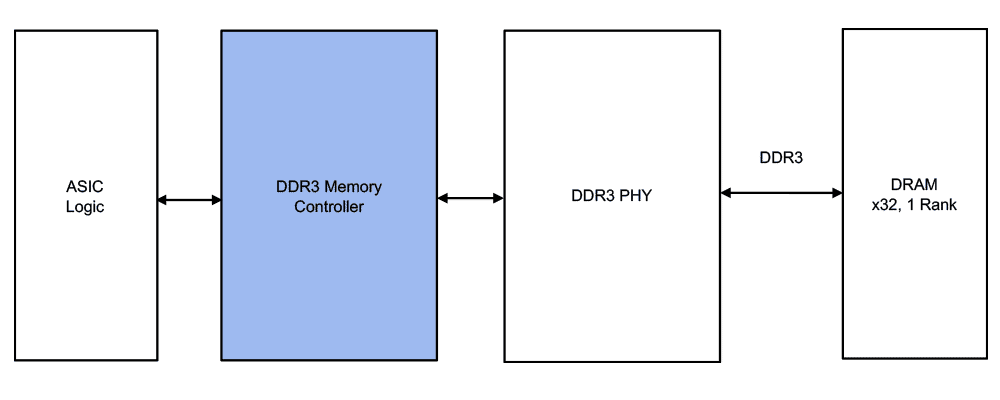

How a DDR3 Interface Subsystem works

The Rambus DDR3 controller maximizes memory bus efficiency via Look-Ahead command processing, bank management, auto-precharge and additive latency support. The core is DFI compatible and supports a range of interfaces to user logic. The Rambus DDR3 controller can be paired with 3rd-party or customer PHY solutions.

Solution Offerings

Features

Deliverables

Services

Features

- Maximizes bus efficiency via look-ahead command processing, bank management, auto-precharge and additive latency support

- Latency minimized via parameterized pipelining

- Achieves high clock rates with minimal routing constraints

- Supports full-rate and half-rate clock operation

- Multi-mode controller support

- Full run-time configurable timing parameters and memory settings

- Supports ODT, dynamic ODT, 2T timing and write leveling calibration

- DFI compatible

- Full set of Add-On cores available

- Minimal ASIC gate count

- Broad range of ASIC and FPGA platforms supported

- Delivered fully integrated and verified with target PHY

Deliverables

- Core (source code)

- Testbench (source code)

- Complete documentation

- Expert technical support

- Maintenance updates

Services

Engineering Design Services:

- Customization

- SoC integration

Protocol Compatibility

| Protocol | Data Rate (Mbps) Max. | Application |

|---|---|---|

| DDR3 | 800 to 2133 | IoT, Edge |