MIPI CSI-2 Controller Core

Home > Interface IP > MIPI Controller IP > MIPI CSI-2 Controller Core

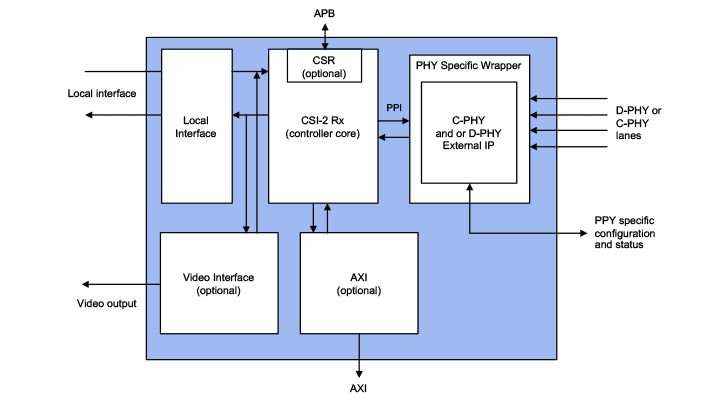

The Rambus MIPI CSI-2 controller core is optimized for high performance, low power and small size. The core is fully compliant with the CSI-2 standard and implements all three layers defined therein: Pixel to Byte Packing, Low Level Protocol, and Lane Management. For automotive safety-critical applications, an ASIL-B version of the core is available and includes a Safety Manual, Design Failure Mode & Effects Analysis (DFMEA) and Failure Mode, Effects and Diagnostic Analysis (FMEDA).

MIPI® Sensor Solutions for Autonomous Driving

Sensors drive the algorithms that interpret the data enabling ADAS driving systems. High bandwidth global shutter cameras, and low-latency, low-power radar, lidar and sonar sensors’ streaming data leverage MIPI CSI-2® technologies to meet challenging design requirements. This session will discuss how highly configurable MIPI CSI-2 based PHY and Controller sub-system solutions can be tailored to address the needs of autonomous driving. Example customer use cases will illustrate the implementation of these MIPI CSI-2 solutions.

Solution Offerings

- Fully MIPI CSI-2 standard compliant

- 32, 64 and 128-bit core widths

- Transmit and Receive versions

- Supports 1-8, 9.0+ Gbps D-PHY data lanes

- Supports 1-4, 6.0+ Gsym/s C-PHY lane (trio)

- Supports all data types

- Easy-to-use pixel-based interface

- Optional video interface

- Enhanced features available: LRTE, USL, D-PHY ECM

- Delivered fully integrated and verified with target MIPI PHY

- Complete FPGA-based demonstration system available

- Optional ASIL-B Ready safety deliverables

- Core (source code)

- Testbench (source code)

- Complete documentation

- Expert technical support

- Maintenance updates

Engineering Design Services:

- Customization

- SoC integration

Protocol Compatibility

| Protocol | Data Rate (Gbps) | Application |

|---|---|---|

| CSI-2 | 9.0+ | Mobile, IoT, Automotive |