On-chip Noise Monitor

Home > Interface IP > On-Chip Noise Monitor

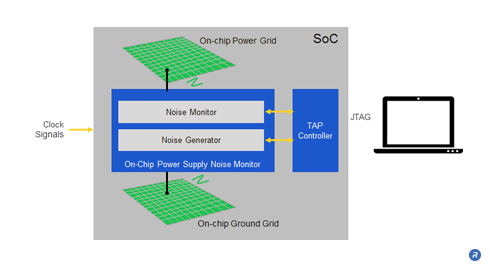

Our On-chip Power Supply Noise Monitor is a compact IP block designed to give SoC designers a better understanding of the effects of power supply noise on circuit performance, and ultimately, improve the chip quality and reduce time-to-market. It is embedded directly into the SoC and accurately measuring power supply noise in low-power, high-performance interfaces and electronic systems.

How the On-Chip Noise Monitor works

Our On-Chip Power Supply Noise Monitor has been developed to overcome the characterization challenges of low-power, high-performance interfaces and electronic systems. It is a compact IP block embedded on-chip and works in conjunction with our LabStation™ Validation Platform to enable noise measurements directly on the chip. This is important because, one of the technical challenges in the development of low-power, high-performance complex IPs and electronic systems is accurately characterizing power supply noise and understanding how that noise affects circuit performance.

The conventional approach of hand-probing outside the chip package is slow, error prone, and often misses high-frequency noise that is filtered out by the package. These difficulties only increase with further miniaturization of packaging technology in smartphones and tablets including integrated package-on-package (PoP) and 2.5D/3D packages.

The Noise Monitor accurately captures high-frequency noise components and uses sampled measurements combined with post-processing to measure noise in both the time and frequency domains. It also includes a Noise Generator that provides a controllable noise source that operates over a wide range of frequencies and amplitudes. The generator can be used in conjunction with noise and jitter measurements to extract power distribution network impedance (ZPDN) and power supply noise induced jitter (PSIJ) sensitivity.

Memory Systems for AI and Leading-Edge Applications

Thanks to rapid advancements in computing, neural networks are fueling tremendous growth in AI for a broad spectrum of applications. Learn about the memory architectures, and their relative advantages, at the heart of the AI revolution.Solution Offerings

- Available for TSMC40G/LP

- Voltage resolution: 200µV/LSB

- Frequency resolution: 1MHz

- Fully-characterized hard macro

- Complete design views:

- Behavioral model

- Full documentation:

- Integration guide

- ASIC/DFT manufacturing guidelines

- CDL netlists (.cdl)

Resources

Videos