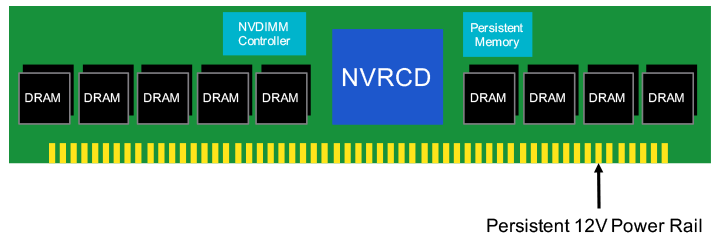

Non-Volatile DDR4 Registering Clock Driver (NVRCD)

Home > Memory Interface Chips > DDR4 DIMM Chipset > Non-Volatile DDR4 Registering Clock Driver (NVRCD)

The Rambus NVRCD is the industry’s 1st JEDEC-standard persistent memory register clock driver (NVRCD) in full production for use with NVDIMM-N and emerging NVDIMM-P solutions. This chipset is our complete application-specific standard product (ASSP) solution that is reliable and cost effective. This NVRCD enables persistent memory R-DIMMs and LR-DIMMs operating at speeds up to DDR4-3200.

How NVRCD for NVDIMM Works

Register Clock Drivers (RCD) buffer and retime command, address, and clock signals from the host CPU. This reduces signal loading on the system controller by isolating the DRAM and is a common practice used in datacenter and other applications where there is an increased need for high-speed memory.

Rambus’ NVRCD is the market’s first full-production ASSP clock driver that meets or exceeds all JEDEC DDR4 performance specifications and is operational up to DDR4-3200. It also meets or exceeds all JEDEC RCD2 (rev 93) operation requirements and supports JEDEC LCOM interface which saves FPGA pins usage. This NVRCD is for NVDIMM-N products, which specifically implements non-volatile solid-state memory, such as NAND Flash, and DDR4 DRAM on the same DIMM, but also enables future emerging technologies like NVDIMM-P architectures.

Persistent memory usage on the DIMM has many use cases for hyperscale, high-performance and high-capacity data centers. These applications include: latency reduction, power reduction, metadata storage, in-memory databases, software-defined server RAID, reduced processing load during unexpected failures and more.

Data Center Evolution: DDR5 DIMMs Advance Server Performance

Driven by a confluence of megatrends, global data traffic is increasing at an exponential rate. For example, 5G networks are enabling billions of AI-powered IoT devices untethered from wired networks. Nowhere is the impact of all this growth being felt more intensely than in data centers. Indeed, hyperscale data centers have become the critical hubs of the global data network. DDR5 DRAM will enable the next generation of server systems providing the massive computing power of hyperscale and enterprise data centers. Learn about the benefits of DDR5 memory and the design considerations for implementing DDR5 DIMMs.Solution Offerings

- Meets or exceeds all JEDEC DDR4 performance specifications

- Meets or exceeds all JEDEC RCD2 (Rev 93) operational requirements including

- Control Geardown

- Command-Address Latency (CAL)

- Qn Delay Gen2 functions

- Supports JEDEC standard DDR4 NVRCD LCOM interface

- Saves at-least 26 FPGA pins

- Supports JEDEC Byte Addressable Energy Backed Interface (BAEBI) Rev 2

- Supports speeds up to DDR4-3200

- MR snooping

- CSR command execution

- DRAM RD/WR command replication

- NVC access RCD at any time

- LCK clock multiplication/division

- LCK clock synchronization

- High performance LCOM runs at 500 MHz and supports host disconnect/reconnect, RCD initialization, DRAM initialization and other sequences

- High Performance Servers

- High Performance Workstations

- High Capacity Storage Systems

- In-memory databases

- Big Data Analytics

- Hyperscale data centers

- Persistent memory architectures

- Tiered storage and caching

High Speed Memory Interface Chipsets Let Server Performance Fly

The demands on server performance continue to increase at a tremendous pace. New requirements from large in-memory databases that are powering today’s cloud services and advanced analytics tools are arriving just as the impact of Moore’s Law is starting to slow. One key new opportunity is for high-speed server memory interface chipsets, which enable high-speed memory performance without compromising on memory capacities. Companies looking to optimize their server memory architecture designs, and improve their overall server performance and reliability, should give serious consideration to optimized DDR4 memory interface chipsets, which enhance the performance of server memory modules.Resources

News

Videos