[Updated on June 10, 2024] AI学習データセットは増加し続けており、テラバイト規模の帯域幅をサポートするアクセラレータが求められています。高いメモリ帯域幅と電力効率に優れたソリューションを提供するHBM3Eは、AI学習ハードウェアの有力な選択肢となっています。

その理由については、以下ブログをご覧ください。.

目次:

HBM3E メモリーとは?

2022年1月に発表されたHBM3は、高性能2.5D/3Dメモリアーキテクチャである高帯域幅メモリ(HBM)の最新世代です。以前のバージョンと同様に、HBM3は1,024ビットのワイドデータパスを採用しています。6.4ギガビット/秒(Gb/s)で動作するHBM3は、819ギガバイト/秒(GB/s)の帯域幅を提供します。HBM3Eは、同じ機能セットを備えながら、9.6Gb/sまで拡張されたデータレートを提供します。優れた帯域幅、大容量、コンパクトなフットプリントにより、高度なAIワークロードに最適なメモリソリューションとなっています。

2.5D/3D アーキテクチャとは?

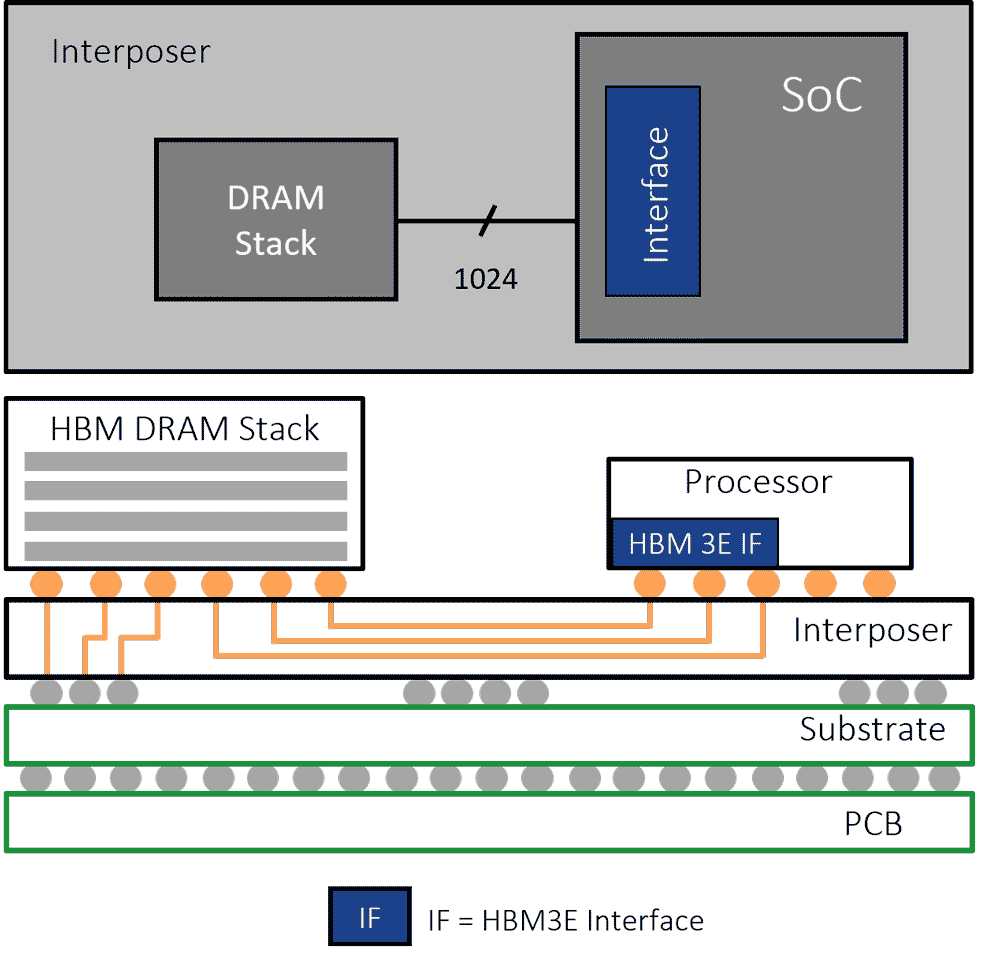

「3D」の部分は分かりやすいでしょう。HBMメモリは、パッケージ化されたデバイス内に3DスタックされたDRAMです。「2.5D」とは、HBMメモリデバイスがGPUやAIアクセラレータなどのプロセッサチップに接続される方法を指します。各HBMメモリデバイスとプロセッサ間のデータパスには、1,024本の「ワイヤ」、つまりトレースが必要です。コマンドやアドレス、クロックなどを追加すると、必要なトレースの数は約1,700に増加します。

1,000本を超える配線は、標準的なPCBでは到底サポートできません。そのため、メモリデバイスとプロセッサを接続するための中継としてシリコンインターポーザが使用されます。集積回路と同様に、シリコンインターポーザには微細な間隔で配線をエッチングできるため、HBMインターフェースに必要な配線数を実現できます。HBMデバイスとプロセッサは、インターポーザ上に2.5Dアーキテクチャと呼ばれる方法で実装されます。

HBM3E Uses a 2.5D/3D Architecture

HBM3E はHBM2E, HBM2 または HBM (Gen 1)とどう違うのか?

HBM3は、HBM規格の第3世代にあたります。世代が進むにつれて、データレート、3Dスタックの高さ、DRAMチップの密度が向上してきました。これは、仕様がアップグレードされるたびに、より高い帯域幅とより大きなデバイス容量を実現していることを意味します。

HBMは1Gb/sのデータレートで発売され、最大8段の16Gbデバイスを3Dスタックで構成できました。HBM3では、データレートは最大6.4Gb/sまで拡張され、デバイスは32Gb容量のDRAMを16段スタックで構成できます。主要DRAMメーカーは、データレートを9.6Gb/sまで引き上げるHBM3Eデバイスを発表しました。

HBMデバイスの高密度化と並行して、チップアーキテクトはAIアクセラレータおよびGPU設計において、より高いアタッチレートの実現を目指しています。6.4Gbpsで動作するHBM3デバイス6個を搭載した設計では、4.9TB/sのメモリ帯域幅を実現します。

| Generation | Data Rate (Gb/s) | Bandwidth per Device (GB/s) | Stack Height | Max. DRAM Capacity (Gb) | Max. Device Capacity (GB) |

|---|---|---|---|---|---|

| HBM | 1.0 | 128 | 8 | 16 | 16 |

| HBM2 | 2.0 | 256 | 8 | 16 | 16 |

| HBM2E | 3.6 | 461 | 12 | 24 | 36 |

| HBM3 | 6.4 | 819 | 16 | 32 | 64 |

| HBM3E | 9.6 | 1229 | 16 | 32 | 64 |

HBM3Eのさらなる変更

しかし、それだけではありません。HBM3では、HBM2Eに比べて電力、メモリアクセス、RASも強化されています。

- 消費電力:HBM3E/3では、コア電圧がHBM2Eの2Vから1.1Vに引き下げられています。また、HBM3ではIO信号がHBM2Eの1.2Vから400mVに引き下げられています。電圧が低いということは、消費電力も低いということです。これらの変更は、データレートの高速化に伴う消費電力の増加を相殺するのに役立ちます。

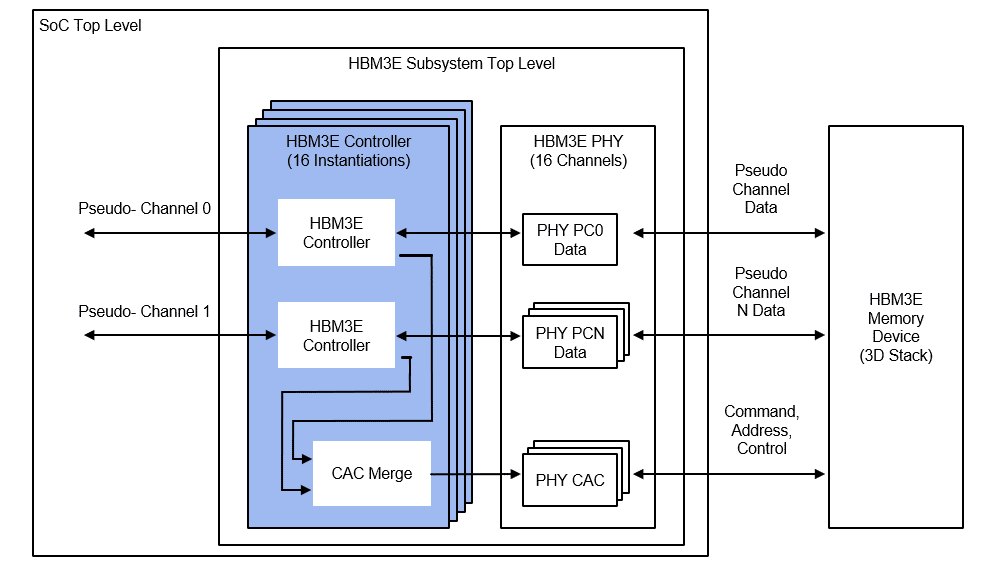

- チャネルアーキテクチャ:HBM3E/3は、1024ビット幅のデータチャネルを16個の64ビットチャネルまたは32個の32ビット擬似チャネルに分割します。これにより、メモリチャネル数がHBM2Eの8個の128ビットチャネルと16個の64ビット擬似チャネルに比べて2倍になり、パフォーマンスが向上します。

- 信頼性、可用性、保守性(RAS): HBM3E/3 では、ホスト側とデバイス側の追加の ECC が導入され、リフレッシュ管理 (RFM) とアダプティブ リフレッシュ管理 (ARFM) のサポートも導入されています。

Rambus HBM3E/3 メモリコントローラコア

高帯域幅と低レイテンシ向けに最適化された Rambus HBM3E/3 メモリ コントローラー コア (HBM3E/3 Memory Controller cores )は、コンパクトなフォーム ファクターと高い電力効率で AI 学習に最大限のパフォーマンスと柔軟性を提供します。

HBM3E Memory Controller Example

Rambus HBM3E/3メモリコントローラコアは、HBM2Eの最大信号速度を2倍以上に向上させ、データレートをデータピンあたり市場をリードする9.6Gbps(標準速度6.4Gbpsをはるかに上回る)に向上させます。このインターフェースは16個の独立したチャネルを備え、各チャネルは64ビットで、合計1024ビットのデータ幅を実現します。最大データレートでは、接続されたHBM3E/3メモリデバイスごとに合計1,229GB/秒、つまり1.23テラバイト/秒(TB/秒)のスループットを実現します。

まとめ

コンパクトで大容量のフットプリントで比類のないメモリ帯域幅を提供する HBM は、AI/ML やその他の高性能コンピューティング ワークロードに最適なメモリとなっています。 Rambus HBM3E/3コントローラコア(Rambus HBM3E/3 Controller cores) は、最大9.6Gb/sの性能を備え、HBM3の拡張ロードマップで業界をリードします。このソリューションにより、設計者は接続されたHBM3E/3メモリデバイスごとに最大1.23TB/sのスループットを実現できます。

Leave a Reply