As the performance demands of personal and enterprise computing continue to rise, memory system designers are challenged to meet the memory speed and capacity requirements needed to address the growing demand. The traditional method of supporting memory system capacity expansion is through the use of a memory bus with a multi-drop topology, which supports multiple devices per data signal. These topologies support upgradeability and multiple modules per memory bus, but can degrade signal integrity and ultimately, the speed the of the memory bus. Point-to-point topologies, which support one device at each end of the signal line, have better signal integrity properties and permit higher bus speeds, but cannot be upgraded with multiple modules. Dynamic Point-to-Point (DPP) technology combines the benefits of multi-drop and point-to-point topologies by enabling upgrade in capacity without degrading signal integrity and memory bus speed.

- Enables capacity expansion at full memory bandwidth

- Support for multiple modules at data rates up to 6.4Gbps

- Dynamically configures memory channel to support multiple modules with the same controller

- Backwards compatible with most standard signaling such as SSTL and RSL

What is Dynamic Point-to-Point Technology?

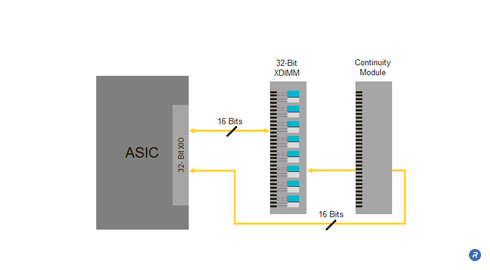

A key benefit of DPP technology is that by providing capacity expansion, DPP technology allows point-to-point upgrades at full memory system bandwidth. DPP technology can be applied to many different types of memory technologies, including DDR4 and beyond. In an example 32-bit DDR3 memory system, the base system configuration has a single memory module, with this module supplying all of the memory bandwidth across the full datapath width. A continuity module occupies the second memory slot, providing electrical continuity that maintains the point-to-point connection across half of the datapath.

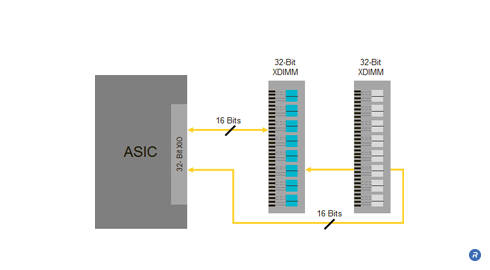

When the continuity module is removed and an expansion module is added, the datapath is reconfigured to supply memory bandwidth from both modules. In this example, each module supplies half of the memory system bandwidth across a different half of the datapath in a point-to-point topology. Using DPP technology, the single 32-bit module is “dynamically rewired” to become a 16-bit module when the second module is added. In order to accomplish this the width of the memory devices on the module must change from x4 DRAMs to X2 DRAMs in the upgraded module configuration. In the x4 mode, each DRAM supplies four bits of data, two bits directly to the ASIC and two bits through the continuity module to the ASIC. When an upgrade module is inserted, the path through the continuity module is broken and the devices switch to x2 mode. In x2 mode, each DRAM supplies two bits of data directly to the ASIC.

Before and after the capacity upgrade, point-to-point signaling is maintained, allowing memory system bandwidth to be maintained. The dynamic rewiring in DPP technology allows the memory system to retain the signal integrity benefits of point-to-point signaling while enabling memory system capacity expansion at full memory system bandwidth. DPP technology can be used in conjunction with FlexPhase technology, together forming a compelling framework for memory system architecture.

Who Benefits?

DPP delivers benefits to system designers, integrators and consumers. The degraded signal integrity and overall memory speed cause by multi-drop topologies can cause significant challenges for system designers. The improved signal integrity that DPP technology provides frees memory bus speeds from multi-drop signaling constraints. DPP technology also allows system designers to increase memory capacity without sacrificing signal integrity. Like system designers, system integrators benefit from the improved signal integrity that DPP technology provides, allowing more robust systems to be created. Finally, consumers benefit from the increased data rates a module upgrades provided by DPP technology, enabling capacity expansion without sacrificing performance.