Conventional, low-speed DRAM systems distribute clock, command, and address signals to multiple DRAMs using a topology in which those signals propagate to all of the DRAMs in the system at approximately the same time. In such systems, the propagation delays on the command and address lines introduce timing skew into the system, thereby limiting the operating frequency of the bus and ultimately impacting the performance of high speed memory systems. In addition, the performance of these topologies is also limited by capacitive loading. Both the flight time skew problem and the capacitive loading issues discussed above through the use of the Fly-by architecture. Fly-by command/address architectures improve signal integrity in memory systems, thus enabling higher per-pin bit rates and systems capable of GHz data rates while maintaining low latency, and avoiding the need for clock-encoding.

- Improves signal integrity and overall system performance

- Simplifies system design with relaxed timing constraints

What is Fly-by Command Address Technology?

Although the skew in the clock, command, and address arrival times at each DRAM is small, the skew becomes significant as clock frequencies continue to increase. In such systems, the frequency limitations on the Command /Address (C/A) bus that result from the skew become a limiting factor in trying to achieve reliable GHz-speed memory operation performance.

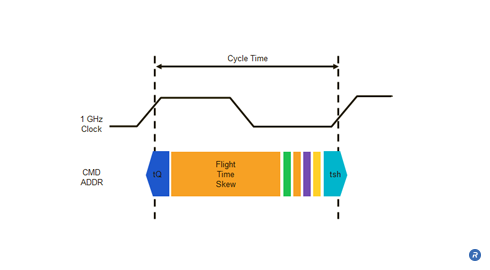

The variability in flight time from the memory controller to the memory devices, or “flight time skew”, can become a significant factor in high frequency systems with short clock periods. As shown, the flight time skew can consume a large portion of the available cycle time such that when operating at speeds greater than 1 GHz, very little time is left for reliable signal set-up and hold times. The issue is further compounded when operating at double data rates.

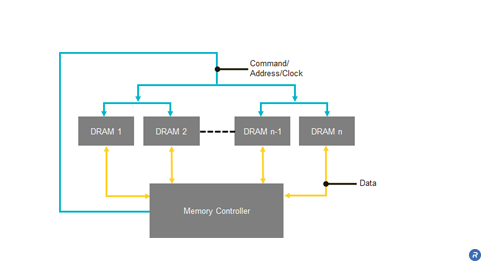

In trying to address the problem of flight time skew, a common solution is to try to match the trace lengths of the signal lines used to convey the command and address signals. One technique that tries to do such trace matching relies on a forked topology. In a forked topology, such as that illustrated below, the command, address, and clock signal traces are routed to a central node and then distributed from the central node to the individual DRAMs. By providing a signal distribution point closer to the DRAMs, the potential variability in trace length is limited to the shorter paths from the central node to the individual DRAMs.

Additionally, the performance of conventional DRAM topologies is constrained by capacitive loading. Adding memory devices to increase memory capacity on the module increases the capacitive loading of the C/A lines, thereby limiting the signaling rate on the C/A line.

Rambus patented innovations address both the flight time skew problem and the capacitive loading issues discussed above through the use of the Fly-by architecture. The Fly-by architecture was incorporated in Rambus DRAM systems as a means to enable increased memory capacity without impacting memory data rates. The Fly-by architecture optimizes the system transmission topology, is tolerant of timing skews and, when used in combination with FlexPhase™ circuit technology, can further manage any skew issues. Fly-by enables point-to-point data lines with scalable capacity without compromising memory data rates.

In the Fly-by architecture the clock, address, and command are transmitted source synchronously to the DRAMs. As shown in the figure above, the clock signal propagates with the address and control information such that those signals arrive together at the interface of each DRAM. However, in this topology, the set of signals propagating on those lines arrives at each DRAM at a slightly different time. As can be seen from the illustration above, the signals will arrive at DRAM 1 shortly before DRAM 2 and so on. Because the arrival times of the signals at the DRAM interfaces are distributed in time, the time at which the signals encounter the input capacitance of each of the DRAMs is similarly distributed, thus reducing the capacitive loading issues discussed above. The reduced capacitive loading enhances the signal integrity and enables higher data rate signaling.

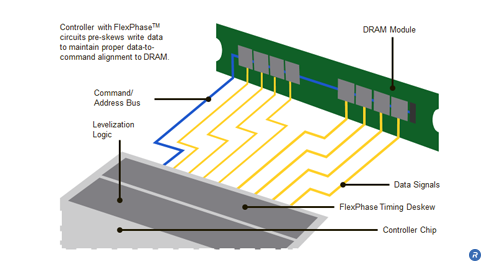

Further increases in data rates can be achieved by employing FlexPhase circuit technology to the data signals at the memory controller. Because the arrival times of the control and address signals at the DRAMs are distributed in time, the resulting data traffic received from the DRAMs on the separate data lines will also be slightly skewed in time. FlexPhase circuitry can be used to de-skew these incoming data signals. FlexPhase circuitry can also be used to pre-skew the data signals driven from the controller to the DRAMs so the data arrives with a well understood timing relationship with respect to the command and address signals.

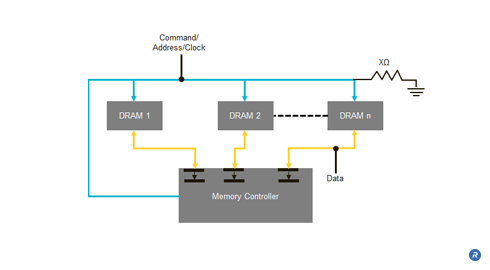

The Fly-by Command Address architecture can also use routing traces on the circuit board that are terminated in order to achieve better controlled impedance on the line than would be realized using other topologies. Additional impedance mismatch reduction can be achieved by having shorter stub lengths from the command/address line to each DRAM device on the memory module. The improved impedance characteristics of the signal lines results in smaller signal reflections and less noise, which in turn enables higher frequency signaling.

In addition to providing higher data rates, another significant advantage of the Fly-by approach is that it is highly scalable in that multiple additional DRAMs can be inserted in a system to meet the needs of the relevant applications. With the added DRAMs, the Fly-by architecture is able to maintain high data rates on the Command/Address/Clock signals, whereas other topologies are limited by flight time skew, capacitive loading and impedance mismatches. Such non-Fly-by topologies often must reduce signaling rates on the Command/Address lines to accommodate the added DRAMs, thereby reducing system performance.

When used with FlexPhase circuit technology, the Fly-by architecture allows designers to relax PCB trace length requirements because the timing variations can be managed on the memory module with the FlexPhase circuit technology. Rambus has also developed Dynamic Point to Point technologies that, when used in combination with Fly-by, enable memory upgrades while maintaining bandwidth.

Who Benefits?

Fly-by architectures enable subsystems that require operational data rates that are significantly greater than those achievable with conventional approaches. Using Fly-by architectures allows designers to relax PCB trace length requirements allowing much simpler and more compact memory sub-system layouts.

In addition, Fly-by architectures provide system benefits by enabling DRAM systems to operate with GHz data rates. This superior DRAM system performance results in improved performance in desktops, notebooks, enterprise servers and storage, HDTVs, gaming systems, and handheld portable devices for end users.