Home > Interface IP > DDR Memory Controller IP

DDR Memory Controller IP

Rambus DDR4 and DDR3 Controllers deliver high-bandwidth, and power efficiency while providing full compatibility with the DDR4 and DDR3 industry standards.

Explore Products

| Version | Maximum Data Rate (MT/s) | Controller |

|---|---|---|

| DDR4 | 3200 | |

| DDR4 Multi-modal* | 2400 | |

| DDR3 | 2133 |

*Supports DDR4, DDR3, LPDDR3 and LPDDR2

DDR Controller IP

| Feature | DDR4 Controller | DDR3 Controller |

|---|---|---|

| Data Rate (MT/s) | 1600 to 3200 | 800 to 2133 |

| Clock Operation | Half-rate and quarter-rate | Full-rate and half-rate |

| Bank Management | Up to 32 banks | Up to 32 banks |

| SDRAM Feature Support | 3DS device configurations Write CRC Data bus inversion (DBI) Fine granularity refresh Additive latency Per-DRAM addressability Temperature-controlled refresh | ODT Dynamic ODT 2T timing Write leveling calibration |

| Interface to Logic | Native or AXI | Native or AXI |

| DFI Compatible | Yes | Yes |

| Multi-mode Controller Support | Yes | Yes |

| Add-On Cores | Multi-Port Front-End Reorder ECC | Multi-Port Front-End Reorder ECC |

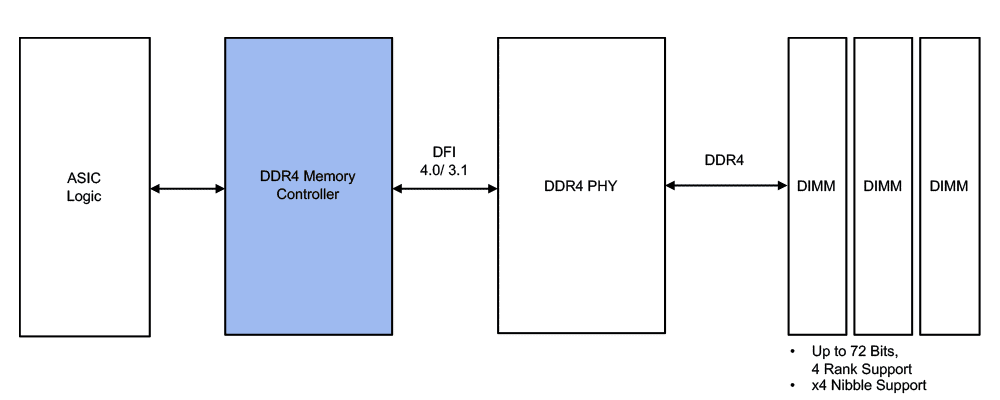

DDR4 Memory Subsystem

The Rambus DDR4 memory delivers industry-leading data rates of up to 3200 Mbps and is compatible with the DDR4 and DDR3 standards.

The Rambus DDR4 controller maximizes memory bus efficiency via Look-Ahead command processing, bank management, auto-precharge and additive latency support. The core is DFI compatible and supports a range of interfaces to user logic. The Rambus DDR4 controller can be paired with 3rd-party or customer PHY solutions.

Deliverables

Services

Deliverables

Controller

- Controller (source code)

- Testbench (source code)

- Complete documentation

Services

Controller

- Expert technical support

- Maintenance updates

- Customization

- SoC Integration

Engineering Design Services:

- Package design

- System board layout

- Statistically-based signal and power integrity analysis