Home > Memory Interface Chips > DDR5 Client DIMM Chipset

DDR5 Client Clock Driver, Power Management IC and SPD Hub Chips

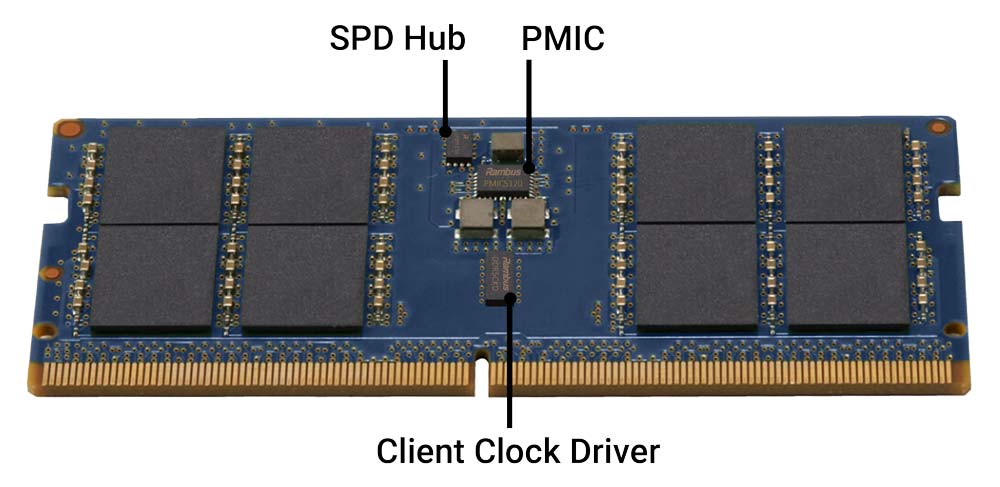

The Rambus DDR5 memory interface chipset for client DIMMs includes the DDR5 Client Clock Driver (CKD), Power Management IC (PMIC) and Serial Presence Detect Hub (SPD Hub). These chips enable the next generation of high-performance desktop and notebook PCs to handle demanding workloads for gaming, content creation and AI.

| Description | Part Number | Product Brief | Applications |

|---|---|---|---|

| 7200 MT/s Client Clock Driver | DR5CKD1Gxx | Client CSODIMM, CUDIMM | |

| Power Management IC PMIC5100 | P1535Gxx | Client SODIMM, CSODIMM, UDIMM, CUDIMM | |

| Power Management IC PMIC5120 | P2535Gxx | Client SODIMM, CSODIMM, UDIMM, CUDIMM | |

| SPD Hub with Internal Temperature Sensor | SPD1605Gxx | Client SODIMM, CSODIMM, UDIMM, CUDIMM, LPCAMM2 |

Rambus DDR5 Client DIMM Chipset Performance

The Rambus DDR5 Client Clock Driver (CKD) enables DDR5 client DIMMs (CUDIMMs and CSODIMMs) to operate at up to 7200 MT/s. Client DIMMs at 6400 MT/s and above employ a CKD as part of their standard architecture to manage jitter and close timing for the synchronous memory system.

The Client Clock Driver retimes and distributes the clock sent from the processor to the DRAM devices on the DIMM. It is a key chip for enabling data rates at 6400 MT/s and above on CSODIMMs and CUDIMMs or in implementations where the DRAM are directly soldiered to the motherboard.

The PMIC5120 receives a high voltage input and steps it down to the voltages needed to power the DRAM and all other chips on module. This architecture supports higher power efficiency and finer grain control of supply currents.

The SPD Hub with integrated temperature sensor enables communication via the I3C bus of important data for system configuration and thermal management.

Ask the Experts: Client Memory Interface Chipsets

In this episode of Ask the Experts, we discuss client chipsets for DIMMs and LPCAMM2 with Carlos Weissenberg, Senior Product Marketing Manager, Memory Interface Chips at Rambus. Topics include: the need for advanced chips to enable higher levels of performance, the role of Client Clock Driver (CKD) and Power Management ICs (PMIC), and how AI applications are driving the need for greater memory bandwidth and capacity.

Data Center Evolution: DDR5 DIMMs Advance Server Performance

Driven by a confluence of megatrends, global data traffic is increasing at an exponential rate. For example, 5G networks are enabling billions of AI-powered IoT devices untethered from wired networks. Nowhere is the impact of all this growth being felt more intensely than in data centers. Indeed, hyperscale data centers have become the critical hubs of the global data network. DDR5 DRAM will enable the next generation of server systems providing the massive computing power of hyperscale and enterprise data centers. Learn about the benefits of DDR5 memory and the design considerations for implementing DDR5 DIMMs.