SPD Hub with Internal Temperature Sensor

Home > Memory Interface Chips > DDR5 DIMM Chipset > DDR5 SPD Hub with Internal Temperature Sensor

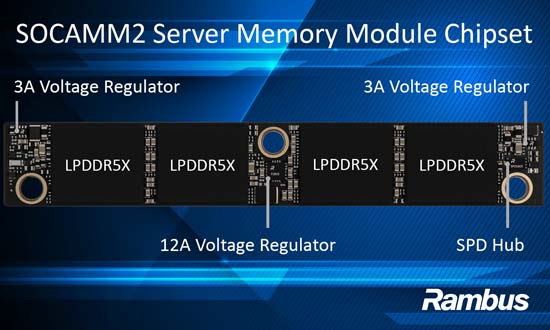

The Rambus SPD Hub (SPD1605Gxx) enables DDR5 Registered DIMMs (RDIMMs), MRDIMMs, Unbuffered DIMMs (UDIMMs and CUDIMMs), Small-Outline DIMMs (SODIMMs and CSODIMMs), LPDDR5 SOCAMM2, and LPCAMM2 memory modules.

How the DDR5 SPD Hub Works

The Rambus DDR5 Serial Presence Detect (SPD5) Hub device contains 1024 bytes of non-volatile memory arranged as 16 blocks of 64 bytes per block. Each block may optionally be write-protected via software command. Write protection for each block may be overridden in an offline programmer environment while overrides are prevented in normal use. The SPD5 Hub device operates from 1.8V nominal power supply input. The SPD5 Hub device is intended to operate up to 12.5 MHz on an I3C Basic bus or up to 1 MHz on an I2C bus. The SPD5 Hub device is intended to interface to I2C/I3C Basic buses which have multiple devices on a shared bus and must be uniquely addressed with fixed addressing on the same bus. The SPD5 Hub device responds to specific pre-defined I2C/ I3C Basic device select codes on a host interface bus. The SPD5 Hub device also incorporates a second local I2C/I3C Basic bus and pass-through of commands from the host bus onto the local bus for addressing of I2C/I3C Basic devices on the local bus (Hub function). The SPD5118-Gxx device incorporates thermal sensing capability which is controlled and read over I2C/I3C Basic bus.

Features of the DDR5 SPD Hub with Internal Temperature Sensor

- I2C and I3C Basic bus serial interface support

- Meets or exceeds all JESD300-5 performance specifications up to 1MHz for I2C and 12.5MHz for I3C Basic bus serial interface

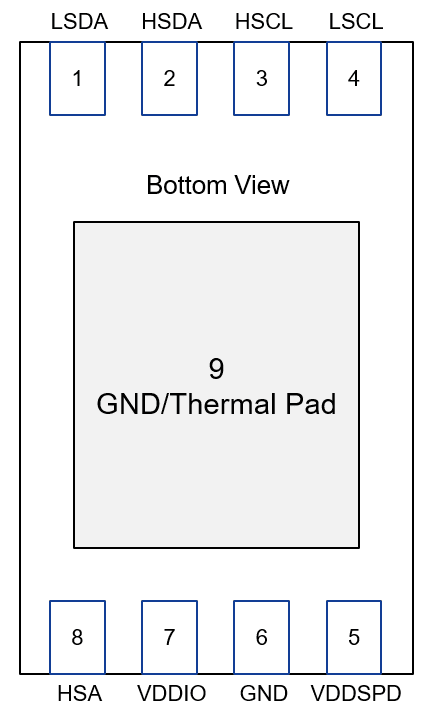

- 9-pin thermally enhanced DFN package, PSON-8, MO-229 var V/W/UCED-3, 2.0 mm x 3.0 mm

- 1024 bytes of non-volatile memory with write protection

- 756 bytes of vendor logging space

- Hub function with up to 8 unique addresses

- Parity error check and packet error check (PEC) function

- In-band Interrupt (IBI) support

- Integrated temperature sensor

- Operational at 1.8V +10%/- 5%

- Dynamic driver switching capability for I3C Basic bus operation between push-pull and open-drain

- Meets or exceeds all JEDEC SPD Hub Device operational requirements

Data Center Evolution: DDR5 DIMMs Advance Server Performance

Driven by a confluence of megatrends, global data traffic is increasing at an exponential rate. For example, 5G networks are enabling billions of AI-powered IoT devices untethered from wired networks. Nowhere is the impact of all this growth being felt more intensely than in data centers. Indeed, hyperscale data centers have become the critical hubs of the global data network. DDR5 DRAM will enable the next generation of server systems providing the massive computing power of hyperscale and enterprise data centers. Learn about the benefits of DDR5 memory and the design considerations for implementing DDR5 DIMMs.