DDR5 Multiplexed Registering Clock Driver (MRCD) and Multiplexed Data Buffer (MDB)

Delivering industry-leading memory bandwidth and capacity

Home > Memory Interface Chips > DDR5 DIMM Chipset > DDR5 Multiplexed Registering Clock Driver (MRCD) and Multiplexed Data Buffer (MDB)

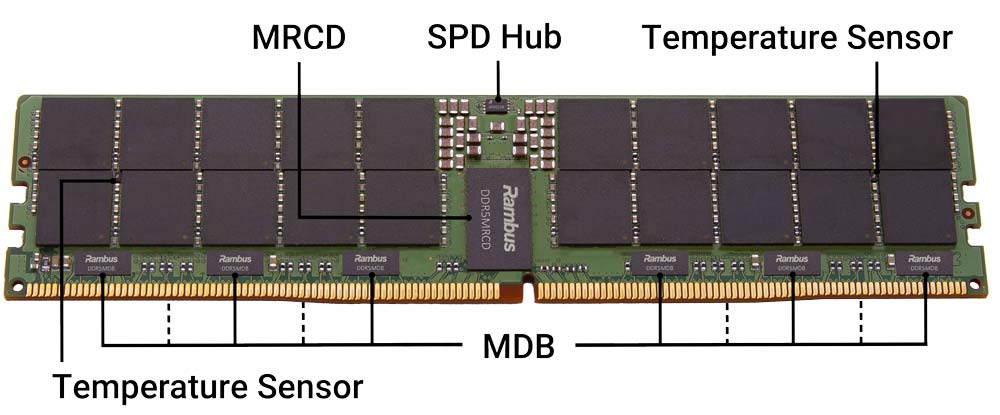

The Rambus DDR5 Multiplexed Registering Clock Driver (MRCD) and Multiplexed Data Buffer (MDB) enable industry-standard DDR5 Multiplexed Rank DIMMs (MRDIMMs) operating at data rates up to 12,800 MT/s.

Each DDR5 MRDIMM 12800 requires one MRCD and ten MDB chips to multiplex the memory channel. The MRCD and MDB will also support a Tall MRDIMM form factor with four ranks of DDR5 DRAMs for double the capacity of a dual-rank RDIMM in a cost-effective manner.

Expanding Server Memory Capabilities with Multiplexed Rank DIMM (MRDIMM) Technology

As per socket compute density increases, the amount of directly accessible, low-latency memory bandwidth and capacity to adequately feed data to the multiple cores needs to scale accordingly. Scaling memory bandwidth by increasing raw DRAM component bandwidth or by increasing the number of memory channels has challenges and is reaching limits. JEDEC has unveiled the development of a new DIMM technology called Multiplexed Rank Dual Inline Memory Modules (MRDIMM) to address the bandwidth challenge.

Data Center Evolution: DDR5 DIMMs Advance Server Performance

Driven by a confluence of megatrends, global data traffic is increasing at an exponential rate. For example, 5G networks are enabling billions of AI-powered IoT devices untethered from wired networks. Nowhere is the impact of all this growth being felt more intensely than in data centers. Indeed, hyperscale data centers have become the critical hubs of the global data network. DDR5 DRAM will enable the next generation of server systems providing the massive computing power of hyperscale and enterprise data centers. Learn about the benefits of DDR5 memory and the design considerations for implementing DDR5 DIMMs.