MIPI Controller IP

Home > Interface IP > MIPI Controller IP

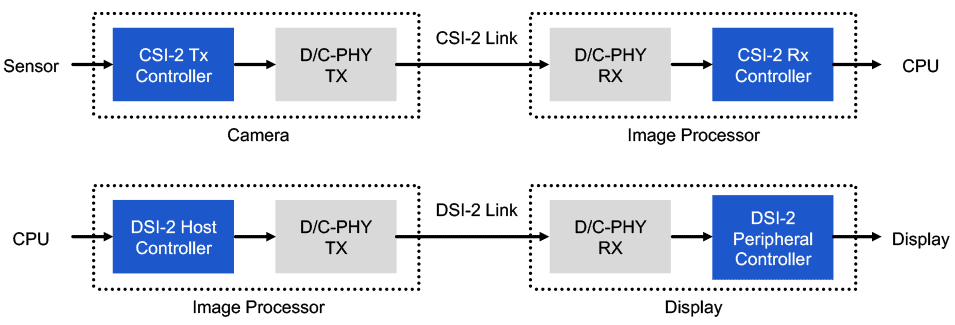

MIPI CSI-2 & MIPI DSI-2 Controller IP

Silicon-proven, high-performance MIPI® CSI-2® and DSI-2SM controller cores are optimized for use in SoCs, ASICs and FPGAs. An available MIPI testbench provides the capability for end-to-end simulations of MIPI designs.

| Solution | Product Brief | Description |

|---|---|---|

| MIPI CSI-2 Tx and Rx | High-performance, low-power, compact CSI-2 Tx and Rx cores. An ASIL-B ready version of the cores is available for automotive safety-critical applications. One specific version of the CSI-2 Tx Controller was ASIL-B certified by SGS to demonstrate compliance. | |

| MIPI DSI-2 Tx and Rx | High-performance, low-power, compact DSI-2 Tx and Rx cores. An ASIL-B Ready version of the cores is available for automotive safety-critical applications | |

| Testbench | Emulates a MIPI device enabling end-to-end simulation of a MIPI design. Separate versions for CSI-2 Tx, CSI-2 Rx, DSI-2 Host (Tx), DSI-2 Peripheral (Rx) are available |

MIPI CSI-2 Controller IP Performance

The Rambus CSI-2 Controller is optimized for high performance, low power and compact area. It is available in 32, 64 and 128-bit core widths. The 32-bit core width supports 1-4 D-PHY data lanes (8-bit PPI) and 1-2 C-PHY lanes (16-bit PPI). The 64-bit core width supports 1-8 D-PHY data lanes (8-bit PPI) and 1-4 C-PHY lanes (16-bit PPI). The 128-bit core width supports 1-8 D-PHY data lanes (16-bit PPI) and 1-4 C-PHY lanes (32-bit PPI).

The core is fully compliant with the CSI-2 standard and implements all three layers defined therein: Pixel to Byte Packing, Low Level Protocol, and Lane Management. Separate transmit (Tx) and receive (Rx) versions of the core are available. The core’s local interface provides an easy-to-use pixel-based interface (single, double, quad, octal pixel wide). A Hsync/Vsync video interface is also available.

The latest generation of Rambus CSI-2 Controller also supports CSI-2 v4.2+ features such as Universal Serial Link (USL), Latency Reduction and Transport Efficiency (LRTE) and D-PHY ECM (Embedded Clock Mode).

For automotive applications, optional features facilitate the support for Camera Service Extension (CSE) and native automotive long reach PHYs.

MIPI DSI-2 Controller IP Performance

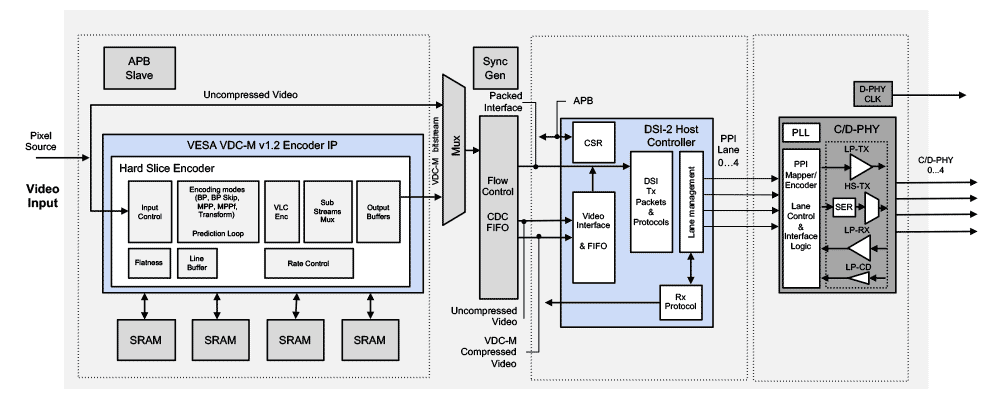

The Rambus DSI-2 Controller core is optimized for high performance, low power and compact area. It is available in 32 and 64-bit core widths. The 32-bit core width supports 1-4 D-PHY data lanes (8-bit PPI) and 1-2 C-PHY lanes (16-bit PPI). The 64-bit core width supports 1-4 D-PHY data lanes (8-bit PPI) and 1-4 C-PHY lanes (16-bit PPI).

The core is fully compliant with the DSI-2 standard and implements all three layers defined therein: Pixel to Byte Packing, Low Level Protocol, and Lane Management. Separate Host (Tx) and Peripheral (Rx) versions of the core are available. The core’s native interface provides easy-to-use data and control/status packet interfaces. The data interface includes an optional DSI-2 video interface. The interface supports command and video modes and all data types.

Latest DSI-2 v2.2+ features such as Video Hybrid Mode (VHM), Adaptive Refresh Panel (ARP), Extended Vertical Front Porch (EVFP), Variable Refresh Rate (VRR) are now supported.

Rambus CSI-2 and DSI-2 cores are delivered fully integrated and verified with the user’s target D/C-PHY. Please contact Rambus for a complete list of supported PHYs. The cores are also provided with the CSI-2 or DSI-2 Testbench which provides a Bus Functional Model.

Related Products

The Rambus MIPI DSI-2 Controller can be combined with the Rambus VESA DSC and VDC-M cores to make a complete display IP solution. Find out more about the Rambus VESA video compression IP cores.

MIPI Drives Performance for Next-Generation Displays

Download this white paper to learn how MIPI DSI-2 interface and VESA® DSC visually lossless compression technologies can meet the challenges of next-generation displays.

MIPI CSI-2 Controller

- Fully CSI-2 standard compliant

- 32, 64 and 128-bit core widths

- Transmit and Receive versions

- Supports 1-8, 9.0+ Gbps D-PHY data lanes

- Supports 1-4, 6.0+ Gsym/s C-PHY lane (trio)

- Supports all data types

- Easy-to-use pixel-based interface

- Optional video interface

- Enhanced features available: LRTE, USL, D-PHY ECM

- Delivered fully integrated and verified with target MIPI PHY

- Complete FPGA-based demonstration system available

- Optional ASIL-B Ready safety deliverables

MIPI DSI-2 Controller

- Fully DSI-2/DSI standard compliant

- 32 and 64-bit core widths

- Host (Tx) and Peripheral (Rx) versions

- Supports 1-4, 9.0+ Gbps D-PHY data lanes

- Supports 1-4, 6.0+ Gsym/s C-PHY lane (trio)

- Supports all data types

- Easy-to-use native interface

- Optional video interface

- Enhanced features available: VHM, ARP, EVFP, VRR

- Delivered fully integrated and verified with target MIPI PHY

- Complete FPGA-based demonstration system available

- Optional ASIL-B Ready safety deliverables

- Core (source code)

- Testbench (source code)

- Complete documentation

- Expert technical support

- Maintenance updates

- Engineering Design Services

- Customization

- SoC integration