Home > Security IP > Anti-Counterfeiting > CryptoFirewall Verifier and Consumable Core

Security

CryptoFirewall Verifier and Consumable Core

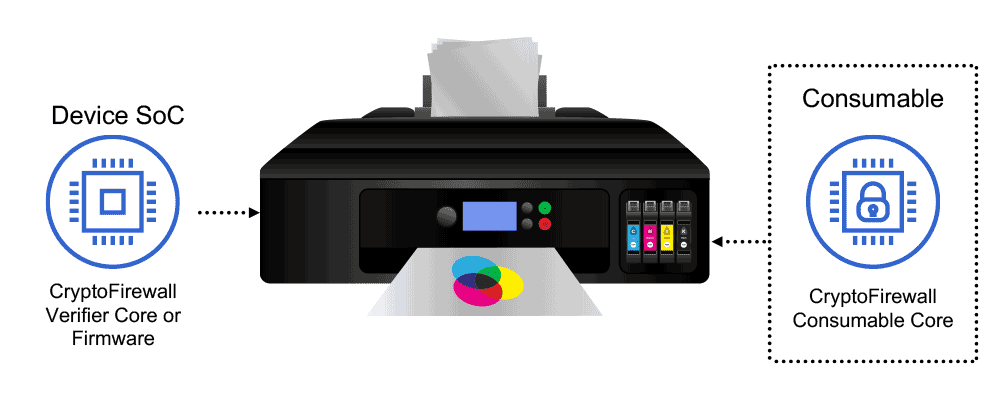

How CryptoFirewall Verifier Core works

The Verifier core is a robust, anti-counterfeiting hardware core designed to provide authentication with the highest level of tamper resistance.

The core can be used in conjunction with the CryptoFirewall Consumable core as part of a complete consumable protection system. It integrates into the device SoC and communicates to the CryptoFirewall Consumable core to authenticate and verify system integrity of the consumable or peripheral.

The Verifier core monitors the balances of the usage counters within the Consumable core, denying authentication once the balance reaches zero.

Anti-Tampering Technologies

The design of chip anti-tamper protection needs to adapt and scale with rising threats. Adversaries range from high school hackers to well-funded state actors. Given the threats, it’s useful to think about anti-tamper countermeasures as a hierarchy of safeguards that parallel the type, effort and expense of attacks. Watch this webinar to learn the eleven kinds of tampering attacks and their required skills and resources, and countermeasures for each of these attacks.

How CryptoFirewall Consumable Core works

Using field-proven, integrated anti-tamper security technologies, the Consumable core works in conjunction with either the CryptoFirewall Verifier core or Verifier firmware to provide consumers and manufacturers assurance of authenticity.

Secure device authentication: Each consumable or peripheral contains a low-cost security chip with the Consumable core that communicates with either a CryptoFirewall Verifier core or with Verifier firmware on the system-side SoC to authenticate and verify system integrity.

Secure usage authentication: The core contains usage counters with balances to authorize and track usage. Balances can be securely decremented with each use, and counters cannot be reset without a strict authentication process.

The Importance of Chiplet Security

Chiplets are gaining significant traction as they deliver numerous benefits beyond what can be accomplished with a monolithic SoC in a time of slowing transistor scaling. However, disaggregating SoCs into multiple chiplets increases the attack surface which adversaries can exploit to penetrate safeguards to data and hardware. With chiplets, the risks of hardware-based trojans and exploits such as man-in-the-middle attacks all rise. To realize the many benefits of chiplets, designers should use a design for security approach, and implement security safeguards anchored in hardware.

Solution Offerings

Part of a complete solution to protect against a broad range of attacks including:

- Software bug vulnerabilities

- Reverse engineering

- Glitching/fault induction

- Power analysis (SPA/DPA)

- Test/debug mode exploits

- Protocol attacks

- Microprobing

- Cryptanalysis

- Focused ion beam analysis

- Imaging/microscopy

- Software emulation

- Insider attacks

Secure device authentication

Secure usage authentication

Gate-level netlist targeted to vendor-specified cell library

Full technical documentation:

- Interface specifications

- Integration guides

- Validation guides

- Manufacturing test and personalization specs

Test and Verification:

- Verification models

- Emulation boards

- Functional verification tests

- System and validation tests

Resources

News