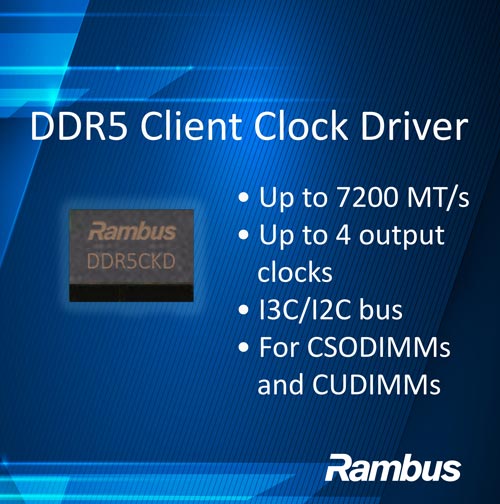

The Rambus Client Clock Driver (CKD) enables DDR5 CUDIMMs and CSODIMMs to operate at state-of-the-art data rates of up to 7200 Megatransfers per second (MT/s) and deliver breakthrough performance in next-generation AI PCs.

Rambus Expands Industry-Leading Memory Interface Chip Offering to High-Performance PCs with DDR5 Client Clock Driver

Highlights:

- Leverages broad server memory expertise to address the growing requirements of AI, gaming and content creation in desktop and notebook PCs

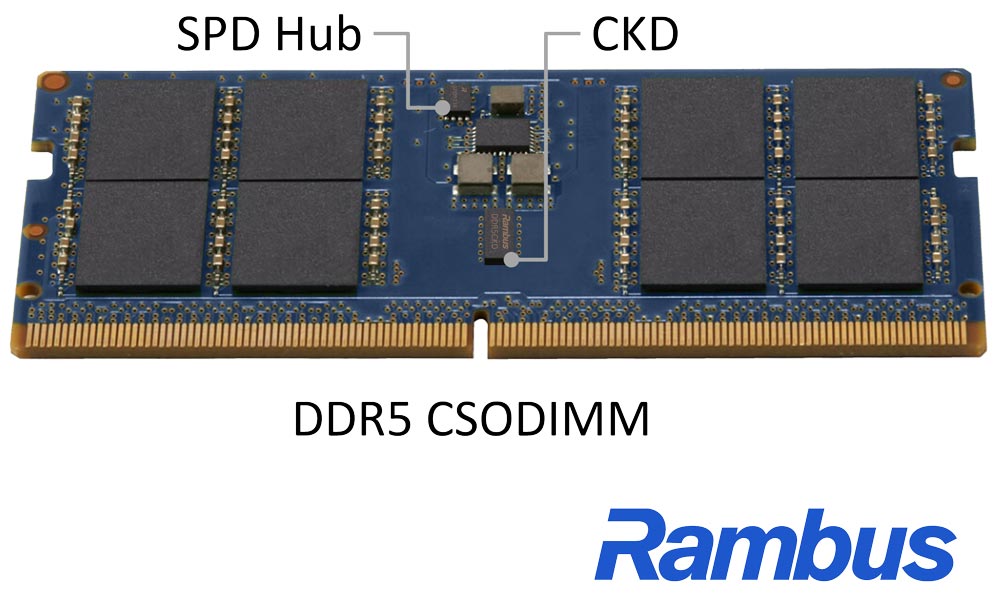

- New client product offering includes DDR5 Client Clock Driver and SPD Hub

- Enables state-of-the-art DDR5 client DIMMs with operation up to 7200 MT/s

SAN JOSE, Calif. – July 29, 2024 – Rambus Inc. (NASDAQ: RMBS), a premier chip and silicon IP provider making data faster and safer, today announced the availability of its DDR5 Client Clock Driver (CKD) for next-generation, high-performance desktops and notebooks. The Rambus DDR5 CKD and SPD Hub are part of a new client memory interface chip product offering that brings server technology advancements to the client market. Leveraging over 30 years of memory system expertise, the Rambus DDR5 CKD enables new client DIMMs (CSODIMMs and CUDIMMs) to operate at state-of-the-art data rates of up to 7200 Megatransfers per second (MT/s), and deliver breakthrough performance in next-generation PCs.

“As advanced technologies first developed for the data center proliferate to the client space, increasingly powerful PCs will take gaming, content creation and AI to new levels,” said Rami Sethi, SVP and general manager of Memory Interface Chips at Rambus. “This new DDR5 Client Clock Driver is the latest addition to our growing line up of chip solutions that enable breakthrough memory performance across the computing landscape, and bring more value to our customers.”

In addition to the CKD, Rambus DDR5 memory interface chips include Gen1 to Gen4 RCDs, Power Management ICs (PMICs), Serial Presence Detect (SPD) Hubs and Temperature Sensors for leading-edge servers. As data rates continue to rise, signal integrity (SI) and power integrity (PI) management become increasingly vital. With over 30 years of high-performance memory experience, Rambus is renowned for its SI/PI expertise. This expertise helps enable DDR5 memory interface chips to deliver superior signal integrity and power efficiency at higher yield for server and client DIMMs.

More Information:

Learn more about the Rambus DDR5 CKD at rambus.com/memory-interface-chips/ddr5-client-dimm-chipset/ddr5-ckd.

Ask the Experts: Securing AI

Ask the Experts: PCI Express 7.0 Interface IP

AI 2.0 Driving Demand for Memory Performance

[July 24 @ 11am PT] Hear from IDC guest speaker, Jeff Janukowicz, and Rambus’ John Eble, as they set the market context and provide adoption expectations for Generative AI and DDR5 memory.

PKE-IP-85 Public Key Engine Family Product Brief

The Rambus SCA-resistant PKE-IP-85 family of Public Key Engine cores provide semiconductor manufacturers with superior public key cryptography acceleration. The cores are easily integrated into ASIC/SoC and FPGA devices, offer a high-level of resistance to Differential Power Analysis (DPA), and, optionally, offer detection of Fault Injection Attacks (FIA).