Junko Yoshida, Chief International Correspondent at UBM Electronics, says Rambus is entering the fabless chip business with the launch of its server memory interface chipset

Terabyte Bandwidth Initiative (1TB) Memory Demo

Rambus Senior Engineering Manager Arun Vaidyanath demonstrates the latest Rambus test chip running in 3 modes: high-speed differential, GDDR5, and DDR3. Groundbreaking memory technologies developed by Rambus enable signaling at 20 gigabits per second (Gbps) while maintaining best-in-class power efficiency, and up to 12.8 Gbps for single-ended signaling.

Why Do I Invent?

We asked some select Rambus inventors to share their views on what motivates them to invent and whether they consider the act of inventing a verb or a noun. Check out what they had to say. Learn more about our inventors here.

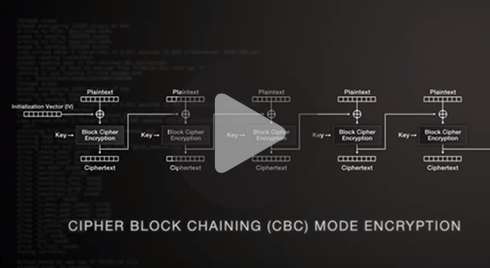

Side-Channel Analysis Demo: Mobile Device

Mobile devices use cryptographic keys to protect sensitive information. At Rambus Cryptography Research, we set out to test mobile devices to see how secure these operations might be. Leakage signals can be picked up by a probe that responds to the magnetic field coming from the device. Gary Kenworthy, Senior Principal Engineer at Rambus Cryptography Research, show a side-channel analysis demo.

To learn more about DPA Countermeasures, please click here.

Side-Channel Analysis Demo: FPGA Board

Elke DeMulder, Senior Research Scientist for Rambus Cryptography Research, demonstrates how field programmable gate arrays (FPGAs) can be compromised by side-channel attacks. Learn more about our DPA Countermeasures here.

Rambus Noise Monitor demo

Our On-Chip Power Supply Noise Monitor has been developed to overcome the characterization challenges of low-power, high-performance interfaces and electronic systems.

- « Go to Previous Page

- Page 1

- Interim pages omitted …

- Page 170

- Page 171

- Page 172

- Page 173

- Page 174

- Interim pages omitted …

- Page 331

- Go to Next Page »