5G connections to hit 1.4 billion by 2025

Juniper Research analysts are forecasting 1.4 billion 5G connections by 2025, an increase from just 1 million – upon commercial launch of 5th generation wireless

Home > Memory PHYs > Page 10

Juniper Research analysts are forecasting 1.4 billion 5G connections by 2025, an increase from just 1 million – upon commercial launch of 5th generation wireless

Rambus has validated interoperability between its HBM2 PHY and Northwest Logics’ HBM2 Memory Controller Core. The combined HBM2 solution is designed to support high-performance networking

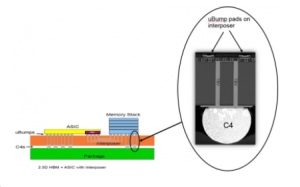

2Tbps multi-lane HBM2 PHY Earlier this month, GLOBALFOUNDRIES demonstrated silicon functionality of a 2.5D packaging solution for its high-performance 14nm FinFET FX-14 integrated design system

GLOBALFOUNDRIES has demonstrated silicon functionality of a 2.5D packaging solution for its high-performance 14nm FinFET FX-14™ integrated design system for application-specific integrated circuits (ASICs). According

Semiconductor Engineering’s Ed Sperling and Jeff Dorsch recently wrote an article about the challenges of chip design in the age of the IoT. As Sperling

Samsung ramps volume production of 8GB HBM2 Earlier this month, Samsung confirmed an increase in production volume of its 8-gigabyte (GB) High Bandwidth Memory-2 (HBM2)