Sarvagya Kochak, a senior product marketing manager at Rambus, recently penned an article for Semiconductor Engineering that explores the concept of enabling higher system performance with NVDIMM-N. According to Kochak, the shift from the traditional enterprise data center to the cloud is driving significant demand for increased bandwidth and lower latencies.

This demand, says Kochak, is fundamentally reshaping traditional memory, storage, network and computing architectures. Indeed, although the semiconductor industry has been innovating to meet the needs of these new architectures, it continues to grapple with a waning Moore’s Law that is most significantly impacting memory and compute scaling.

“For example, we’re no longer seeing CPU speeds increasing at the same rate. To get around this bottleneck, CPU vendors continue to add an ever-increasing number of cores to improve performance,” he explains. “This creates its own challenge, because additional cores must be fed with more data if they are to be effectively utilized. However, as DRAM scaling is slowing, DIMM capacities have not been increasing at the rate needed.”

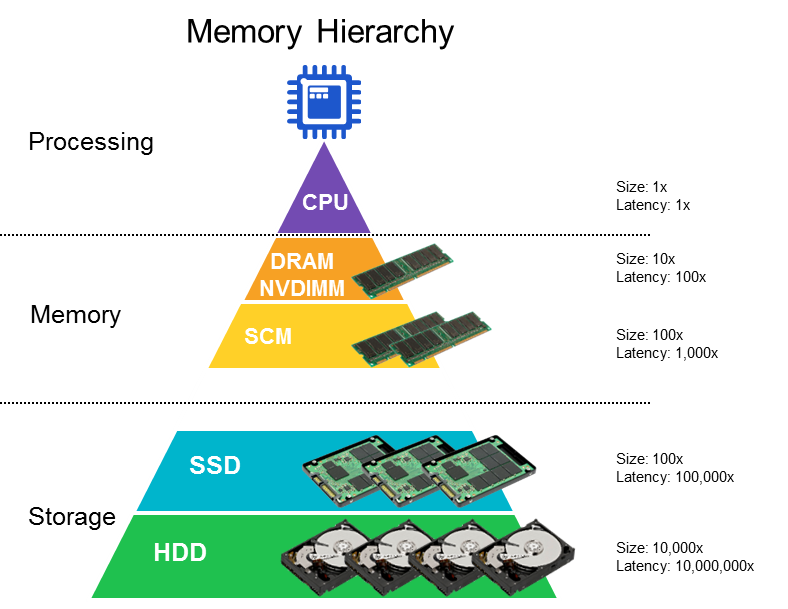

As a result, he emphasizes, there is a need for an alternative to DRAM, which is why the industry is eyeing multiple next-generation memory solutions that have the potential to disrupt the existing memory and storage hierarchy. However, the industry has yet to field a viable alternative to DRAM.

“Some have considered the idea of using NAND flash as system memory to increase memory capacity. NAND, unfortunately, has three orders of magnitude higher latency compared to DRAM, which can lead to inefficient utilization of the memory channel and reduced overall system performance,” Kochak elaborates.

“New RRAM/PCM storage class memories (SCM) promise to be revolutionary – yet it seems unlikely that any memory will come close to DRAM performance. Moreover, it’s not clear when these memories will be available as DIMMs in mass production at a reasonable price point.”

Consequently, system and software architects are rethinking the standard memory-storage subsystems in an effort to extract all the performance they possibly can with technologies that are currently available.

“Application, OS and software stacks are all designed with the underlying assumption that memory is volatile and the contents in DRAM can be lost. Complex mechanisms are used to ensure that if there is a power failure, little to no data is lost,” Kochak continues. “Although this comes at the cost of performance, the industry has come to accept it as a tradeoff. With NVDIMMs, it is possible to accelerate system performance by making memory persistent and eliminating the aforementioned tradeoff.”

The first incarnation of NVDIMM, says Kochak, is NVDIMM-N, which is perhaps best described as battery-backed DRAM. Essentially, NVDIMM-N operates just like a standard DRAM DIMM when accessed by the CPU. However, when there’s a power failure, data is immediately moved from the DRAM to backup NAND on the DIMM itself. This ensures the data in memory is never lost. When the system boots back up, the state is maintained without requiring any complex software.

“Today, NVDIMM-N products are used to increase the performance (i.e. transactions/sec) of write-latency sensitive applications, effectively providing a persistent storage paradigm with DRAM performance,” he adds. “Other applications and use cases include high-availability storage systems and appliances, persistent metadata and object stores, in-memory and traditional databases, high-performance computing (HPC), unstructured data management and genomics.”

In addition to NVDIMM-N, says Kochak, the industry is eyeing NVDIMM-P, a new high-capacity persistent memory module for hyper scale data centers. More specifically, NVDIMM-P would allow the host to access both the DRAM and a secondary SCM on the DIMM to enable systems with high capacity and persistent main memory – further reducing the memory-storage performance and capacity gap.

“From our perspective, NVDIMM-N acts as a vital stepping stone to ensure the success of future SCM and persistent memories on the memory channel. With industry-wide efforts ongoing to standardize persistent memory programming models, platforms and interfaces, we can indeed imagine a time in the future where developers and system architects are going to wonder how we ever managed to get by with volatile system memory,” he concludes.