Rambus’ DDR4 PHY and Arm’s CoreLink DMC-620 Dynamic Memory Controller

Today, we announced the validated interoperability of Rambus’ DDR4 PHY and Arm’s CoreLink DMC-620 Dynamic Memory Controller. Together, these IP blocks offer speeds of up to 3200 Mbps, the highest performance memory speed available on the market.

More specifically, Arm’s CoreLink DMC-620 Dynamic Memory Controller is a fast, single-port Coherent Hub Interface (CHI) that transfers data from its CoreLink CMN-600 (Coherent Mesh Network) to Rambus’ DDR4 memory PHY, the latter of which is fully compliant with JEDEC’s DDR4 and DDR3/3L/3U standards. In addition, the Rambus DDR4 memory PHY and Arm CoreLink DMC-620 are both DFI 4.0 compliant, facilitating seamless interoperability between the PHY and memory controller.

According to Hemant Dhula, vice president of product of the Rambus Memory and Interfaces Division, the interoperable IP blocks provide a verified solution for chip designers, reducing design time and improving time-to-market for demanding data center and communications applications.

“With rising chip design and IP integration costs, these pre-validated solutions from Rambus and Arm provide customers with an easy path to implementation and the peace of mind of a proven solution,” said Dhula. “Rambus strives to work with companies like Arm that are leaders in the IP ecosystem to deliver high-quality, comprehensive solutions to the market.”

Jeff Defilippi, senior product manager, Infrastructure Business Unit, Arm, expressed similar sentiments.

“Design teams face complex challenges in scaling the number of computing cores for advanced datacenter SoCs, while minimizing integration and testing time to ensure faster time-to-market,” Defilippi explained. “Our collaboration with Rambus removes another degree of difficulty in designing purpose-built SoCs, resulting in higher-performing systems built for the most demanding cloud and enterprise workloads.”

A closer look at Rambus’ DDR4 memory PHY

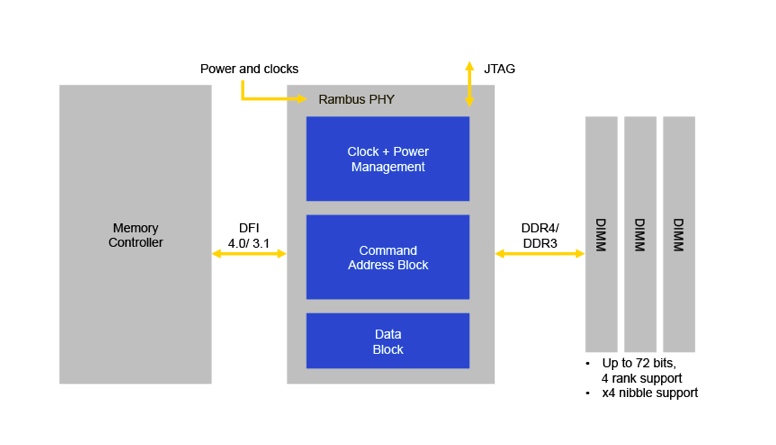

Our DDR4 memory PHY consists of a command/address (C/A) macro cell and data (DQ) macro cells configured to create a 72 bits wide channel.

Key features include:

- Support for multiple channel configurations from x16 through x72 per channel

- Autonomous initialization (PHY independent mode)

- Support for single channel, 1 up to 4 ranks

- Selectable low-power operating states

- DFI 4.0 and 3.1 compliant for easy integration with memory controller

- Programmable output impedance and on-die termination

- Available in North-South, East-West and Corner configurations

- ZQ calibration of output impedance and on-die calibration

- Utilizes standard 8-layer 602011- or 13- metal layer stack.

- Supports package-on-package and C4 flip-chip packaging options

- Register interface for state observation

- Test traffic generation and error checking for in-situ test

- LabStation™ software environment for system level bring-up, characterization and validation

Interested in learning more about Rambus’ DDR4 PHY? You can visit our product page here.