Home > Emerging Solutions > Smart Data Acceleration

Emerging Solutions

Smart Data Acceleration

A research program focused on improving the performance and power efficiency of next generation data centers in the age of Big Data

Improved Performance

DRAM delivers higher bandwidth and lower latency versus solid state disk

Enhanced Power Efficiency

High memory capacity reduces the time and power spent moving data

Accelerated Computing

FPGAs enable parallel offloading and acceleration of compute tasks close to dataSmart Data Acceleration

Our Smart Data Acceleration (SDA) research program is focused on tackling some of the major issues facing data centers and servers in the age of Big Data. The SDA Research Program has been exploring new architectures that are optimized for applications such as Big Data Analytics, and is targeting significant improvements in performance and power efficiency.

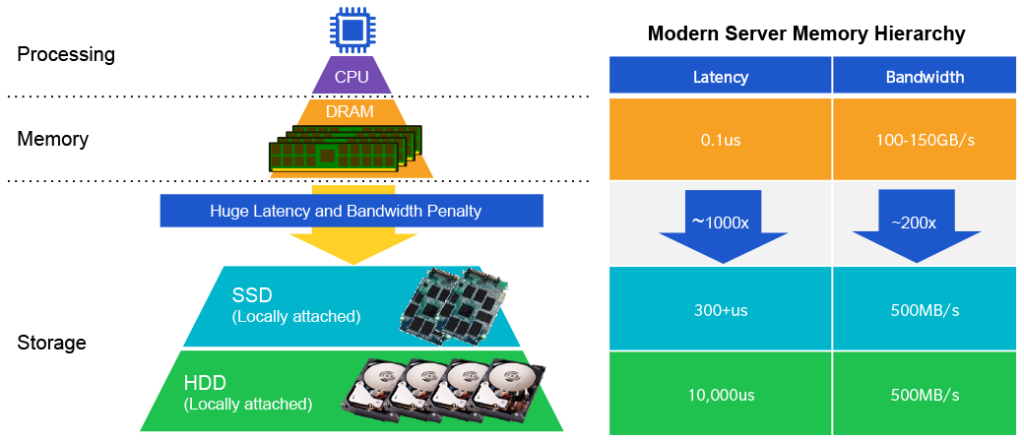

Pervasive connectivity and new usage models are creating an explosion of data, and emerging applications such as real-time analytics, in-memory data bases, financial services, ad serving, and genome sequencing are all demanding instant access to exceedingly large sets of information. These new paradigms of accessing data have caused traditional server and data center architectures to fall out of balance, resulting in low CPU utilization due to a shortage of critical resources such as memory capacity. In some cases, the imbalance between processor cores and memory capacities results in servers running out memory capacity long before the CPU utilization ever becomes an issue. As a result, the CPU is forced to access the disk subsystem in order to access increasingly large data sets, requiring it to cross the large latency and bandwidth gap between memory and storage when processing these large data sets. The result is decreased system performance and power efficiency, and increased Total Cost of Ownership (TCO).

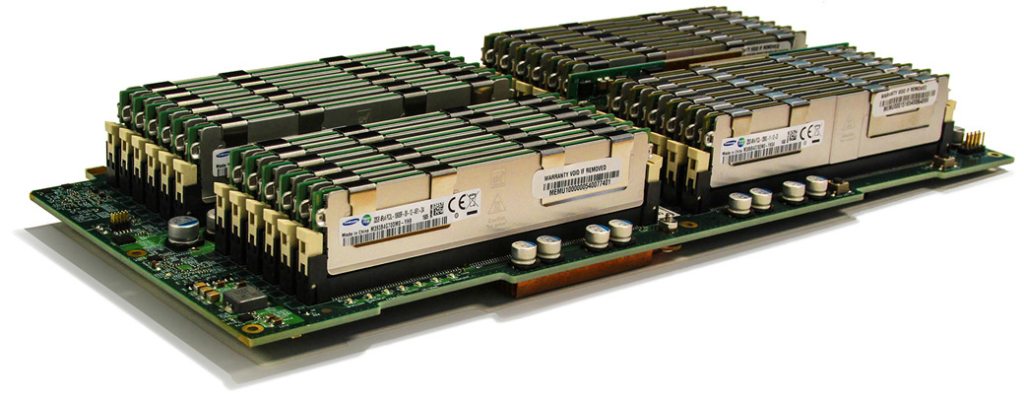

In order to investigate ways to address these challenges, we have created the SDA engine and SDA platform which include software, firmware, FPGAs and large amounts of memory that can be harnessed in different ways to meet varying application needs. The SDA engine combines an FPGA and 24 DIMM sockets into a building block that places flexible computing capabilities next to high memory capacity. At the platform level, multiple SDA engines can be aggregated together into a solution that scales compute and memory capacity as needed by applications. The platform is being used to investigate system architectures that optimize data movement, enhance system performance, and improve power efficiency.

Smart Data Acceleration Engine

The key research areas for improving system performance and power efficiency include:

- Utilizing large amounts of DRAM rather than Solid State Disk (SSD) to reduce latency under load and improve application performance;

- Minimizing data movement by significantly increasing memory capacity which reduces the time and power spent moving data back and forth across the network; and

- Utilizing compute offload and acceleration through the use of FPGAs located close to the memory storing the data.

With benchmarking under way on the SDA platform, this program is well positioned to deliver key technologies and architectures for future data center needs.