LabStation Validation Platform

Home > Interface IP > LabStation Validation Platform

Bring-up and validation of the advanced SoCs is increasingly difficult in today’s fast-paced technology lifecycle. Developed with these challenges in mind, the LabStation platform includes software and hardware to provide a straightforward and accurate method for testing chips and systems.

How the LabStation Platform works

Design complexity for advanced SoCs rises with each new process node, performance increase, and addition of new IP blocks. Designers are faced with increasing challenges to confidently verify and validate functionality of their chips.

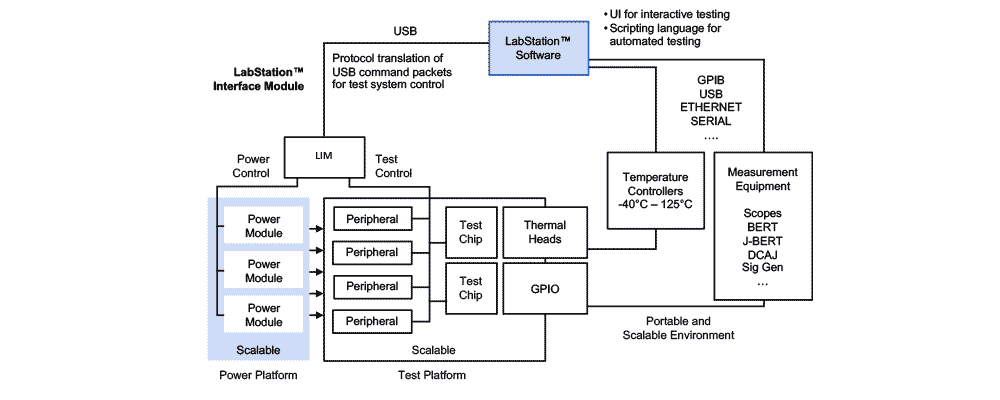

The LabStation Validation platform is a comprehensive tool suite for the rapid bring-up, validation and characterization of complex low-power, high-performance memory and serial link IP. It is designed to be easy to use and improve productivity while providing improved accuracy of test results and confidence is system performance.

The platform features an enhanced user interface to improve the usability and control of IP including access to on-chip circuits, on-board devices, measurement equipment and 3rd party tools. This helps customers validate our R+ Memory and Serial Link PHYs to enhance the quality and reduce time-to-market of their chips and systems. The suite is proven in high-volume applications and offers an effective set of on-chip, automated test tools for validating the designs of advanced memory sub-systems and high-speed serial links for production.

Our LabStation platform provides a fully-automated characterization environment. This simplifies the characterization process and reduces time-to-market by quickly and accurately collecting very high-throughput data across a wide range of temperature and voltage conditions through automated test scripts.

Finally, the LabStation tool suite enables advanced test functionality for chips that utilize 2.5 and 3D packages where taking measurements with a hand probe is inaccurate and, in some instances, impossible to do.

Memory Systems for AI and Leading-Edge Applications

Thanks to rapid advancements in computing, neural networks are fueling tremendous growth in AI for a broad spectrum of applications. Learn about the memory architectures, and their relative advantages, at the heart of the AI revolution.Solution Offerings

- Measures voltage and timing margin eye at target BER (bit error rate)

- Provides on-chip infrastructure for automated measurement of supply noise, power distribution network impedance, and channel step response

- On-chip measurement delivers more accurate results than measurement outside package at high data rate

- Supports testing of 2.5/3D integration and small form-factor packaging

- High-precision power consumption measurement

- User interface includes enhanced access to the component catalog, register detail values, and the command buffer and action log

- Comprehensive chip and system design reviews

- LabStation proprietary software with optimized user interface

- LabStation Interface Module (LIM)

- System test board

- Test chip

- Power delivery board

Inventions

FlexPhase™ Timing Adjustment Circuits

FlexPhase per bit timing adjustment circuits deskew data and clock signals to improve signal integrity and simplify package and PCB system design.

Output Driver Calibration

Output driver calibration allows SoC designers to tune the output signaling to optimal levels in order to improve data rates and system voltage margin.

On Die Termination Calibration

ODT calibration enables higher data rates and superior DRAM device and module performance by establishing the optimal termination value to compensate for variations in process and operating conditions that degrade signal performance.

Resources

Videos