Home > Interface IP > PCI Express Controller IP

PCI Express Controller IP

Rambus silicon-proven, high-performance PCI Express® (PCIe®) 7.0, 6.3, 5.0, 4.0 and earlier generation digital controllers are optimized for use in SoCs, ASICs and FPGAs. These market-leading solutions for high-performance interfaces address AI/ML, data center and edge applications.

| Version | Maximum Data Rate (GT/s) | Controller | Controller with AXI |

|---|---|---|---|

| PCIe 7.0 | 128 | ||

| PCIe 6.3 | 64 | ||

| PCIe 5.0 | 32 | ||

| PCIe 4.0 | 16 | ||

| PCIe 3.1 | 8 | ||

| PCIe 2.1 | 5 |

PCIe Controller IP

| Feature | PCIe 7.0 Controller | PCIe 6.3 Controller | PCIe 5.0 Controller | PCIe 4.0 Controller | PCIe 3.1 Controller | PCIe 2.1 Controller |

|---|---|---|---|---|---|---|

| Data Rate (GT/s) | 128 | 64 | 32 | 16 | 8 | 5 |

| Data Path | Scalable | Scalable | Scalable | Scalable | Scalable | Scalable |

| Topologies Supported | Root Port Endpoint Switch Port Dual-Mode | Root Port Endpoint Switch Port Dual-Mode | Root Port Endpoint Switch Port Dual-Mode | Root Port Endpoint Switch Port Dual-Mode | Root Port Endpoint Switch Port Dual-Mode | Root Port Endpoint Switch Port Dual-Mode |

| Duplex Lane Configurations | x1, x2, x4, x8, x16 | x1, x2, x4, x8, x16 | x1, x2, x4, x8, x16 | x1, x2, x4, x8, x16 | x1, x2, x4, x8, x16 | x1, x2, x4, x8, x16 |

| Backward Compatibility | 6.3, 5.0, 4.0, 3.1 | 5.0, 4.0, 3.1 | 4.0, 3.1 | 3.1 | 3.1, 2.0 | 1.1 |

| Clock Gating/Power Gating | Yes | Yes | ||||

| Advanced RAS | Yes | Yes | Yes | Yes | Yes | Yes |

| Virtual Channel Support | FLIT and non-FLIT mode | FLIT and non-FLIT mode | ||||

| Forward Error Correction (FEC) | Yes | Yes | ||||

| L0p Low Power Mode | Yes | Yes | ||||

| Optional Features | IDE Security, AER, ECRC, ECC, MSI, MSI-X, Multifunction, Crosslink | IDE Security, AER, ECRC, ECC, MSI, MSI-X, Multifunction, Crosslink | AER, ECRC, ECC, MSI, MSI-X, Multifunction, Crosslink | AER, ECRC, ECC, MSI, MSI-X, Multifunction, Crosslink | AER, ECRC, ECC, MSI, MSI-X, Multifunction, Crosslink | AER, ECRC, ECC, MSI, MSI-X, Multifunction, Crosslink P2P |

PCIe Switch, Retimer, DMA and USB4 IP

| Solution | Product Brief | Description |

|---|---|---|

| PCIe 7.0 Retimer Controller | PCIe 7.0 Retimer Controller with CXL Support Provides Highly Optimized, Low-latency Data Path for Signal Regeneration | |

| PCIe 7.0 Switch | PCIe 7.0 Switch is a customizable, multiport embedded switch for PCIe designed for ASIC and FPGA implementations | |

| PCIe 6.3 Retimer Controller | PCIe 6.3 Retimer Controller with CXL Support Provides Highly Optimized, Low-latency Data Path for Signal Regeneration | |

| PCIe 6.3 Switch | PCIe 6.3 Switch is Customizable, Multiport Embedded Switch | |

| PCIe 5.0 Multi-port Switch | Customizable Multi-port Switch, Connects One Upstream Port to Up to 31 Downstream Ports | |

| PCIe Controller for USB4 | PCIe 5 Controller with USB4 Support, with Native Logic Interface Options | |

| PCIe Controller for USB4 with AXI | PCIe 5 Controller with USB4 Support, with AXI Logic Interface Options | |

| PCIe Switch for USB4 | Customizable Switch with USB4 Support, Connects One Upstream Port to Up to 31 Downstream Ports |

PCIe Debug and Test Solutions, and Add-On Cores

| Solution | Product Brief | Description |

|---|---|---|

| INSPECTOR for PCIe 5.0 | Interposer Card for Diagnostic Testing, Exercising and Debug of PCIe Devices at up to 32 GT/s | |

| Gen5HOST | Host Enabling Reference Platform for Prototyping and Development of PCIe 5.0 Devices and Apps | |

| Gen5ENDPOINT | Endpoint Reference Platform for Prototyping and Development of PCIe 5.0 Devices | |

| XpressAGENT | Add-on Core Simplifies Observability and Expedites Debugging of PCIe and CXL subsystems |

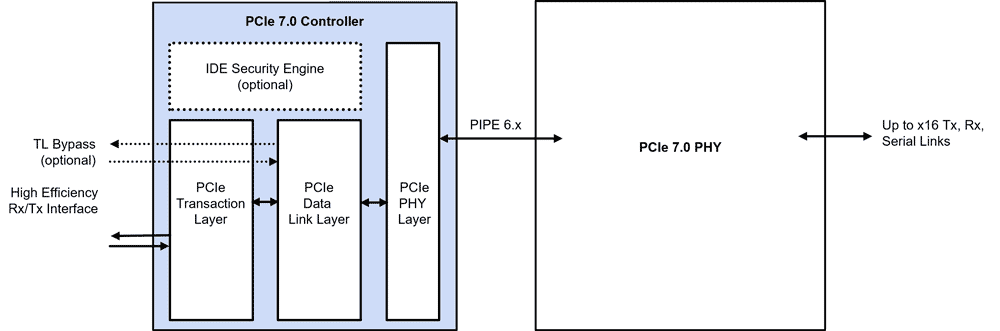

PCIe 7.0 Interconnect Subsystem

The Rambus PCIe 7.0 Controller exposes a highly efficient transmit (Tx) and receive (Rx) interface with configurable bus widths. Designed to satisfy a multitude of customer and industry use cases, the IP can be configured to support endpoint, root port, switch port, and dual-mode topologies, allowing for a variety of use models. The provided Graphical User Interface (GUI) Wizard allows designers to tailor the IP to their exact requirements, by enabling, disabling, and adjusting a vast array of parameters.

Rambus provides integration and validation of the PCIe 7.0 digital controller with the customer’s choice of 3rd-party PCIe 7.0 PHY.

Data Center Evolution: The Leap to 64 GT/s Signaling with PCI Express 6.1

The PCI Express® (PCIe®) interface is the critical backbone that moves data at high bandwidth and low latency between various compute nodes such as CPUs, GPUs, FPGAs, and workload-specific accelerators. With the rapid rise in bandwidth demands of advanced workloads such as AI/ML training, PCIe 6.1 jumps signaling to 64 GT/s with some of the biggest changes yet in the standard.

- Verilog RTL (source code)

- Libraries for functional simulation

- Configuration assistant GUI (Wizard)

- Reference designs

- Complete documentation

- Expert technical support

- Maintenance updates

- Customization

- SoC Integration