CXL™ Consortium member company Rambus participated in a recent Q&A session to discuss CXL’s impact on the evolution of the data center, Rambus’ expertise in CXL interface subsystems, and ideal use cases for CXL technology. Find the full Q&A session with Rambus below.

CXL™ Consortium Member Spotlight: Rambus

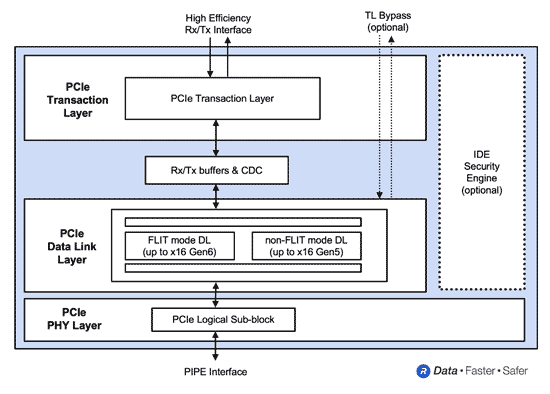

Rambus Delivers PCIe 6.0 Controller for Next-Generation Data Centers

Highlights:

- Pushes performance to 64 GT/s for advanced AI/ML, storage and networking applications

- Implements full PCIe 6.0 feature set with optimized power, area and latency

- Offers state-of-the-art data security with integrated IDE engine

SAN JOSE, Calif. – Jan. 26, 2022 – Rambus Inc. (NASDAQ: RMBS), a premier chip and silicon IP provider making data faster and safer, today announced the availability of its PCI Express® (PCIe®) 6.0 Controller. The PCIe specification is the interconnect of choice across a broad landscape of data-intensive markets including data center, AI/ML, HPC, automotive, IoT, defense and aerospace. Optimized for power, area and latency, the Rambus PCIe 6.0 controller delivers data rates up to 64 Gigatransfers per second (GT/s) for high-performance applications. In addition, the controller provides state-of-the-art security with an Integrity and Data Encryption (IDE) engine that monitors and protects PCIe links against physical attacks.

“The rapid advancement of AI/ML and data-intensive workloads requires that we continue to provide higher data rate solutions with best-in-class latency, power and area,” said Sean Fan, chief operating officer at Rambus. “As the latest addition to our portfolio of industry-leading interface IP, our PCIe 6.0 Controller offers customers an easy to integrate solution that delivers both performance and security for advanced SoCs and FPGAs.”

Key features of the Rambus PCIe 6.0 Controller include:

- Supports PCIe 6.0 specification including 64 GT/s data rate and PAM4 signaling

- Supports fixed-sized FLITs that enable high-bandwidth efficiency

- Implements low-latency Forward Error Correction (FEC) for link robustness

- Internal data path size automatically scales up or down based on max. link speed and width for reduced gate count and optimal throughput

- Backward compatible to PCIe 5.0, 4.0 and 3.0/3.1

- Supports Endpoint, Root-Port, Dual-Mode and Switch port configurations

- Integrated IDE optimized for performance

More Information:

For more information on the PCIe 6.0 Controller, please visit our website. Or, view the PCIe 6.0 specification online.

CXL emerges as memory coherent fabric leader as GenZ Consortium transfers assets

In this 451 Research analysis, the report describes Compute Express Link Consortium’s acquisition of Gen-Z Consortium, seeking “to establish cache-coherent interconnects for processors, memory expansion and accelerators.” Read how this consolidation could positively affect both memory semantic protocols that enable high-speed connectivity to processors, accelerators and memory expansion technologies and the overall market.

Protecting Government Systems: Addressing Growing CyberSecurity Threats With Hardware-Level Security

[Feb 22 @ 11am PT] In this webinar, Adelaide O’Brien, Research Director, Government Digital Transformation Strategies of IDC and Neeraj Paliwal, general manager of Security IP and Rambus, will discuss the need and solutions for protecting systems at the foundational hardware level.

Stopping Stealthy Counterfeit Chips with PUF Helper-Data Images

PUFs, physically unclonable functions, are mixed-signal circuits which rely on variations unique to a specific chip in order to self-generate a digital “fingerprint.” These fingerprints can be used as the basis of cryptographic keys. While that’s useful, the real power of PUFs is leveraging their unclonable transformation function to enable a challenge-response mechanism that can distinguish an authentic chip from a perfect adversarial clone at any time after the original chip is fielded. In this webinar, Scott Best, Technical Director of Rambus Security IP, will describe the methods that PUF helper-data images generated during the chip manufacturing process can be employed to end the risk of undetectable counterfeit chips.

Preventing a $500 Attack Destroying Your IoT Device

Internet of Things (IoT) smart devices numbering in the billions and connected via the internet are increasingly vital to society and the global economy. However, the very “connectedness” that makes IoT devices so valuable can be turned to an enormous liability if these devices are left unprotected from security-related threats. This paper explores the threat environment faced by, and the concepts and methods for securing, IoT devices.