With the rising value of AI/ML spanning training and inference models and data, as well as the AI hardware itself, the threats from adversaries are greater than ever. As such, a security strategy for AI/ML workloads and hardware needs to offer far more than secure boot and authentication. Rambus security expert, Bart Stevens will discuss how a hardware root of trust can be the foundation for AI/ML security through defense in depth, partitioning of secure operations, and state-of-the-art protections from side channel attacks.

Securing Data Center AI/ML Workloads

Selection and Implementation of a PCIe 5.0 Subsystem

The latest generation of the PCI Express, PCIe 5.0, advances performance to 32 GT/s in support of advanced applications including 400G Ethernet. In this webinar, Rambus technology experts Malini Narayanamoorthi and Vinitha Seevaratnam discuss the selection and implementation considerations for PCI Express solutions. A demonstration of the silicon-proven Rambus PCIe 5.0 interface solution consisting of integrated PHY and memory controller will be shown.

Selecting the Right High Bandwidth Memory Solution

An exponentially rising tide of data has led to the development of application-specific silicon to tackle the requirements of demanding workloads such as AI/ML training, Advanced Driver Assistance Systems (ADAS) for automotive, network graphics and HPC. To keep these processors and accelerators fed requires state-of-the-art memory solutions that deliver extremely high bandwidth. Frank Ferro will discuss design and implementation considerations of HBM2E and GDDR6 memory subsystems to address the bandwidth needs of next-generation computing applications.

Next-Generation Displays: An Integrated IP Solution from Mixel, Rambus & Hardent

Displays for next-generation smartphones, AR/VR devices, and automotive systems all require more bandwidth than ever before. Using a combination of VESA Display Stream Compression (DSC) with the MIPI Display Serial Interface (DSI-2) technology, designers can achieve display resolutions up to 8K without compromise to video quality, battery life or cost. This presentation will showcase a fully integrated off-the-shelf display IP solution consisting of Mixel (C-PHY/D-PHY Combo), Rambus (DSI-2 Controller), and Hardent (VESA DSC) IP that delivers state-of-the-art performance. Display use cases addressed by the integrated solution will be discussed. Audience Q&A follows the presentation.

CXL Memory Interconnect Initiative: Enabling a New Era of Data Center Architecture

In response to an exponential growth in data, the industry is on the threshold of a groundbreaking architectural shift that will fundamentally change the performance, efficiency and cost of data centers around the globe. Server architecture, which has remained largely unchanged for decades, is taking a revolutionary step forward to address the growing demand for data and the voracious performance requirements of advanced workloads.

Rambus Advances New Era of Data Center Architecture with CXL™ Memory Interconnect Initiative

- Launches research and development effort to drive architectural shift in data centers with solutions for memory expansion and pooling that enable disaggregated and composable server architectures

- Combines unique expertise in high-speed interfaces, embedded security and server memory buffers to develop breakthrough solutions for next-generation data centers

- Leverages critical building blocks to be provided by PLDA and AnalogX acquisitions, accelerating CXL roadmap and market leadership

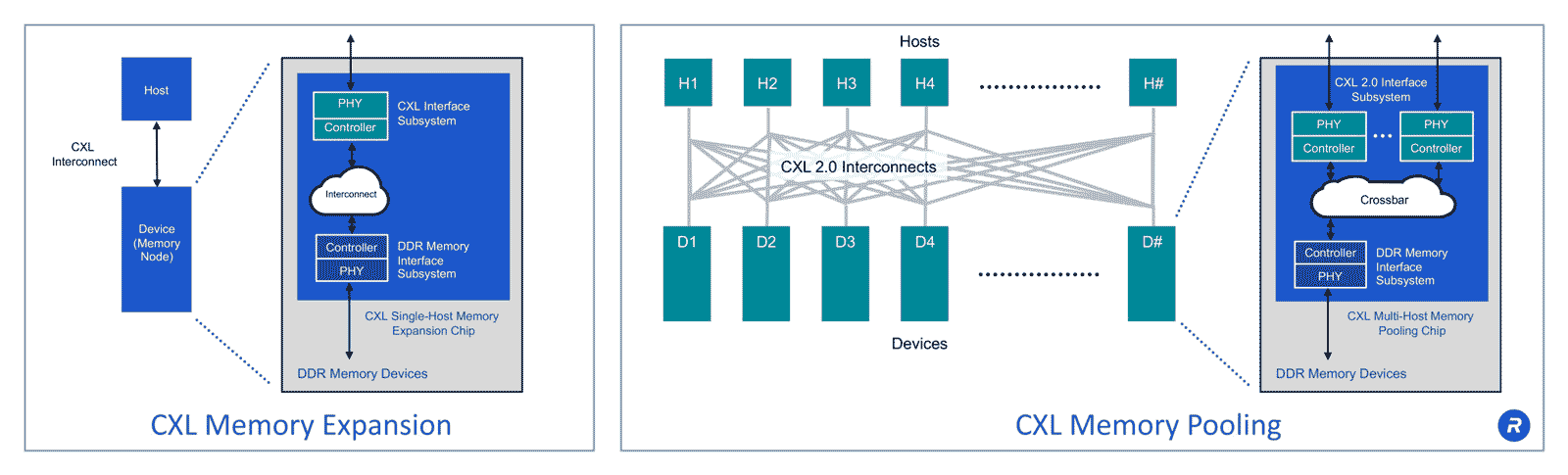

SAN JOSE, Calif. – June 16, 2021 – Rambus Inc. (NASDAQ: RMBS), a provider of industry-leading chips and silicon IP making data faster and safer, today announced the CXL Memory Interconnect Initiative to define and develop semiconductor solutions for advanced data center architectures that maximize performance, improve efficiency and reduce system cost. To support the continuing growth and specialization in server workloads, data center is moving to disaggregated architectures composed from shared and scalable pools of computing and memory resources. Compute Express Link™ (CXL) is a critical enabler of these next-generation disaggregated server architectures. As part of this initiative, Rambus is focusing its initial research and development on semiconductor solutions to support key memory expansion and pooling use cases. The acquisitions of PLDA and AnalogX provide key products and expertise that complement the company’s leadership in server memory interface chips and further accelerate the roadmap for innovative CXL interconnect solutions for next-generation data centers.

“Modern server architectures are taking a revolutionary step forward to support the growing demands of advanced workloads like AI/ML,” said Luc Seraphin, president and CEO of Rambus. “This initiative is highly complementary to our existing server DIMM chipset business and brings together our unique combination of semiconductor and system expertise to develop breakthrough interconnect solutions that improve performance, security, efficiency and TCO for future data centers.”

CXL is an open industry standard interconnect delivering high-bandwidth, low-latency connectivity between dedicated compute, memory, I/O and storage elements within the data center to allow the provision of the optimal mix of each for a given workload. CXL memory expansion and pooling chips are key components for both traditional and disaggregated architectures. Rambus is uniquely positioned to deliver these solutions as a leading provider of the diverse set of required building blocks including:

- CXL and PCIe® PHYs and controllers to interface with host processors and other devices

- DDR memory PHYs and controllers to interface with memory devices

- Advanced cryptographic cores and secure protocol engines to enable secure firmware downloads and protect the links against data tampering and physical attacks with Integrity and Data Encryption (IDE) security

In addition, Rambus has extensive experience delivering memory interface chips at high volume to the server ecosystem and critical system-level expertise to speed time to market. Rambus is engaging with the full ecosystem including cloud, system and memory companies, to accelerate the development and enablement of CXL memory interconnect solutions.

For more information, visit rambus.com/cxlmemoryinterconnects