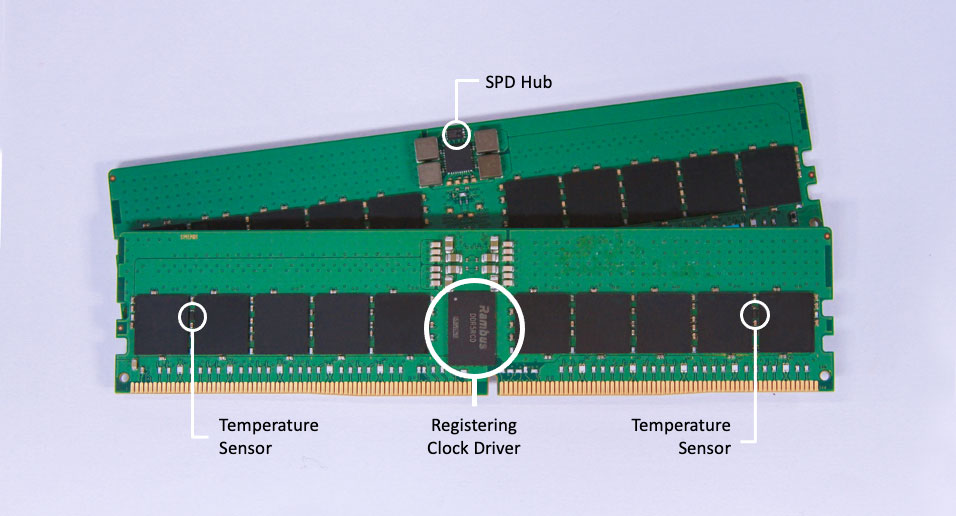

The Rambus Temperature Sensor (TS) TS5110-G1B enables DDR5 Registered DIMMs (RDIMMs), Load Reduced DIMMs (LRDIMMs) and Non-Volatile memory DIMMs (NVDIMMs). Two TS are used per DIMM which along with the SPD Hub’s internal TS provide three points of thermal telemetry.

Rambus Expands Portfolio of DDR5 Memory Interface Chips for Data Centers and PCs

Highlights:

- Introduces SPD Hub and Temperature Sensor as part of server and client DDR5 memory module chipsets

- Complements industry-leading DDR5 RCD delivering state-of-the-art bandwidth and capacity

- Enables enhanced system management and thermal control for improved TCO

SAN JOSE, Calif. – July 18, 2022 – Rambus Inc. (NASDAQ: RMBS), a premier chip and silicon IP provider making data faster and safer, today announced the expansion of its DDR5 memory interface chip portfolio with the addition of the Rambus SPD (Serial Presence Detect) Hub and Temperature Sensor, complementing the industry-leading Rambus Registering Clock Driver (RCD). DDR5 achieves greater memory bandwidth and capacity by employing a new module architecture with an expanded chipset. The SPD Hub and Temperature Sensors improve DDR5 Dual Inline Memory Module (DIMM) system management and thermal control to deliver higher performance within the desired power envelope for servers, desktops and laptops.

“The new performance levels of DDR5 memory place an increased premium on signal integrity and thermal management for server and client DIMMs,” said Sean Fan, chief operating officer at Rambus. “With over 30 years of memory subsystem design experience, Rambus is ideally positioned to deliver DDR5 chipset solutions which enable breakthrough bandwidth and capacity for advanced computing systems.”

“The strong collaboration between Intel and SPD ecosystem partners like Rambus, delivers critical chip solutions for Intel’s next generation DDR5-based systems, scaling server, desktop and laptop performance to new levels,” said Dr. Dimitrios Ziakas, VP of Memory and IO Technologies at Intel. “Our joint efforts to advance DDR5-based computing systems is setting the stage for Intel’s DDR5 advance over multiple generations and the next level of performance for data centers and consumers.”

“DDR5 provides a significant increase in performance for computing systems,” said Shane Rau, research vice president, Computing Semiconductors at IDC. “However, DDR5 memory modules require new components to function, components like SPD hubs and temperature sensors are important components for client and server systems.”

Part of the Rambus server and client DDR5 memory interface chipsets, the SPD Hub and Temperature Sensor combine with the RCD to deliver high-performance, high-capacity memory solutions for DDR5 computing systems. Both the SPD Hub and Temperature Sensor are critical components on a memory module that sense and report important data for system configuration and thermal management. The SPD Hub is used in both server and client modules, including RDIMMs, UDIMMS and SODIMMS, and the temperature sensor is designed for server RDIMMs.

Key features of the SPD Hub (SPD5118) include:

- I2C and I3C bus serial interface support

- Advanced reliability features

- Expanded NVM space for customer-specific applications

- Low latency for fastest I3C bus rates

- Integrated temperature sensor

- Meets or exceeds all JEDEC DDR5 SPD Hub operational requirements (JESD300-5A)

Key features of the Temperature Sensor (TS5110) include:

- Precision thermal sensing

- I2C and I3C bus serial interface support

- Low latency for fastest I3C bus rates

- Meets or exceeds all JEDEC DDR5 Temperature Sensor operational requirements (JESD302-1.01)

Availability and Additional Information

The Rambus SPD Hub and Temperature Sensor are both available today. For additional information, please visit https://www.rambus.com/ddr5-dimm-chipset.

Testing and debugging PCIe 5.0 devices with INSPECTOR

MACsec-IP-361 Product Brief

The MACsec-IP-361 is a plug-and-play solution for adding MACsec on the xMII side of an Ethernet subsystem. It is ideally positioned for designs where the MAC function is tightly integrated with the system-side, for example DMA-MAC Ethernet controllers or switch core IP with integrated MAC modules.

PCIe 6.0 Retimer Controller Product Brief

The Rambus PCIe 6.0 Retimer Controller provides a highly optimized low-latency data path for signal regeneration. It supports retimer chip PHYs via PIPE 5.2/6.1 interfaces. The control plane interface is provided via CSR (AHB-lite). The PCIe 6.0 Retimer Controller is CXL protocol aware and supports links using 64 GT/s and lower data rates of PCIe.

VESA DSC 1.2b Decoder for AMD Xilinx FPGAs Product Brief

The Rambus VESA® Display Stream Compression (DSC) decoder IP core for AMD Xilinx FPGAs deliver visually lossless video compression performance, enabling designers to handle the growing bandwidth requirements of cutting-edge displays with higher resolutions, faster refresh rates, and greater pixel depths.