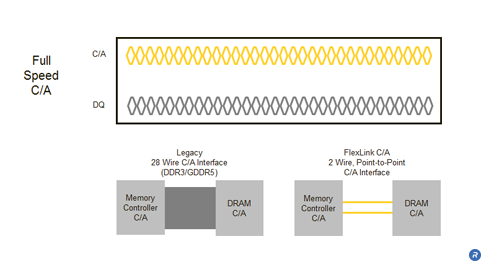

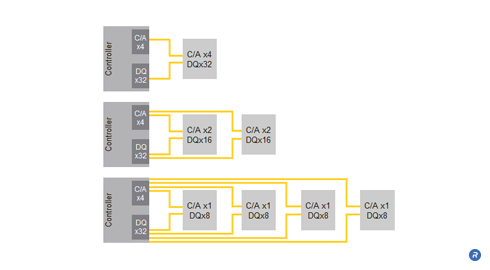

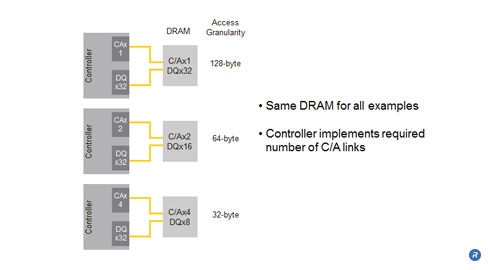

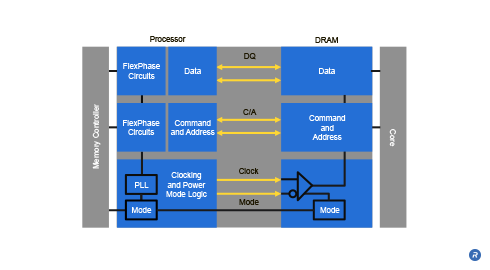

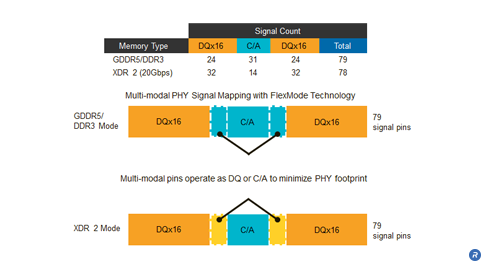

As chip design and fabrication costs continue to rise with each new process node, the ability to integrate flexible, cost-effective multi-purpose interfaces becomes increasingly valuable. Traditional multi-modal implementations combine the worst-case signal pin count for the functional blocks of the interface for each memory type growing the pin count, area and cost of the interface with each mode supported. Rambus’ FlexMode™ Interface technology uses a programmable assignment of signaling pins as either data (DQ), or command/address (C/A), to enable multi-modal functionality while minimizing signal pin count, even when combining different signaling techniques such as single-ended and differential. This enables an SoC memory controller to be implemented in a single package design with no additional signal pin overhead. An SoC using FlexMode™ Interface technology can address a broad range of system requirements, from entry-level to high-end, without additional cost.

- Supports multi-modal functionality– either single-ended or differential—in a single SoC, with no additional pins

- Enables seamless transition to next-gen, high-performance, low-power memory

- Delivers cost-effective flexibility for next-gen chip designs

What is FlexMode Interface Technology?

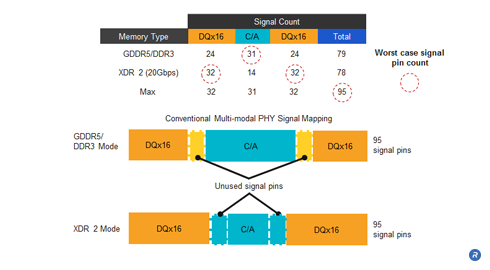

Traditional multi-modal implementations combine the worst-case signal pin count for the functional blocks of the interface for each memory type. When combining functionality of multiple memory types with differing signaling architectures, such as single-ended and differential, this implementation technique can lead to costly design inefficiencies including increased pin count and costs.

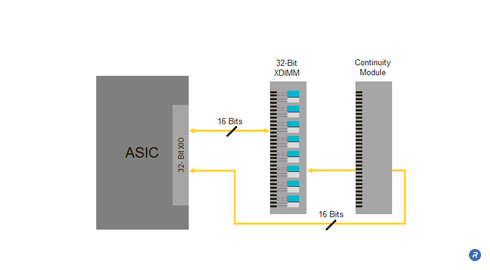

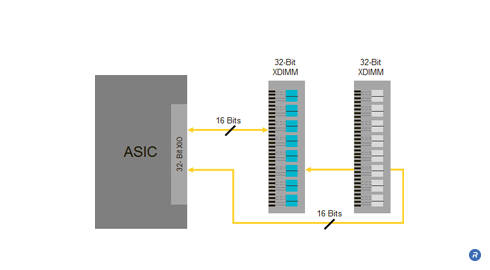

As an example, conventional signal mapping for a 32-bit wide single-ended DDR3 and GDDR5 memory interface combined with a differential XDR™2 memory interface would combine the 64 DQ pins from the XDR 2 memory (worst case DQ) and the 31 C/A pins from the DDR3 interface (worst case C/A) for a total of 95 signal pins (see “Conventional Multi-Modal Interface” diagram). This translates to a 16 signal pin overhead versus the single-ended GDDR5/DDR3 interface.

Who Benefits?

Rambus’ FlexMode™ Interface technology enables multi-modal functionality across differential and single-ended signaling memory types with no additional pin overhead and in a single SoC package design. By advancing data rates to up to 20 gigabits per second in an extremely power-efficient way with XDR 2 memory, and enabling compatibility to current industry-standard memories including GDDR5 and DDR3, FlexMode interface technology removes the technical and business barriers for customers to achieve unprecedented capabilities in their products.

Commercial server managers and consumer end users benefit from the reduced cost of ownership and increased battery life for their end systems and devices.