Hear Rambus and Siemens discuss the background of IDE, the threat models it addresses, and how zero latency IDE’s can provide assurances to CXL adopters. Design and verification engineers and managers won’t want to miss this webinar to understand how to incorporate and validate this essential standard in their designs.

Side-channel attacks explained: everything you need to know

In this blog post, we take an in-depth look at the world of side-channel attacks.

We describe how side-channel attacks work and detail some of the most common attack methodologies. We also explore differential power analysis (DPA), an extremely powerful side-channel attack capable of obtaining and analyzing statistical measurements across multiple operations. In addition, we provide a walkthrough of a DPA attack and explain how different countermeasures with varying levels of effectiveness can be used to prevent side-channel attacks.

Rambus Announces Departure of Chief Financial Officer

Affirms guidance for third quarter fiscal year 2021

SAN JOSE, Calif. – October 13, 2021 – Rambus Inc. (NASDAQ: RMBS) a provider of industry-leading chips and silicon IP making data faster and safer, today announced that Rahul Mathur, senior vice president and chief financial officer (CFO), will resign from Rambus effective November 15, 2021 to pursue another opportunity outside of the semiconductor industry. A formal search has commenced for a new CFO. Keith Jones, current vice president, chief accounting officer and corporate controller at Rambus, will serve as interim CFO and ensure a seamless transition until a replacement has been found.

“Rahul has been an integral part of our transformation as a product company over the last several years. I would like to thank him for his contributions and wish him well in his next opportunity,” said Luc Seraphin, chief executive officer at Rambus. “Rambus is well positioned for continued profitable growth with exciting opportunities ahead of us. Keith brings a wealth of experience to the role, and I am confident he will lead the organization through a successful transition.”

“It has been an honor to work for Rambus,” said Rahul Mathur. “I am proud to have been part of a team that consistently delivered strong financial results and shareholder value, and look forward to watching the continued success of the company.”

Separately, Rambus affirmed its previously issued guidance for the third quarter fiscal year 2021. The company will hold a conference call on November 1, 2021 at 2:00 p.m. Pacific Time to discuss its third quarter fiscal year 2021 results.

Rambus Advances Server Memory Performance with the Industry’s First 5600 MT/s DDR5 Registering Clock Driver

Highlights:

- Boosts DDR5 data rate by 17% while lowering latency and power in 2nd-generation Registering Clock Driver (RCD)

- Provides key enablement of 5600 MT/s DDR5 RDIMMs for server main memory

- Demonstrates sustained Rambus product leadership in DDR5 memory interface chips for next-generation servers

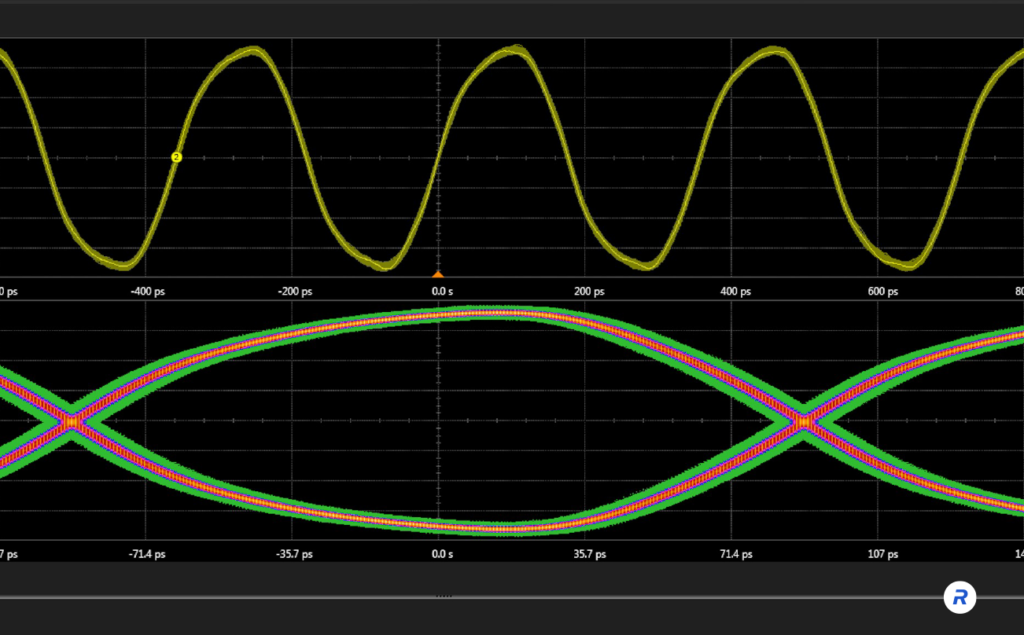

SAN JOSE, Calif. – Oct. 13, 2021 – Rambus Inc. (NASDAQ: RMBS), a premier chip and silicon IP provider making data faster and safer, today announced it is now sampling its 5600 MT/s 2nd-generation RCD chip to the major DDR5 memory module (RDIMM) suppliers. This new level of performance represents a 17% increase in data rate over the first-generation 4800 MT/s Rambus DDR5 RCD. With key innovations, Rambus is able to deliver 5600 MT/s performance at lower latency and power while optimizing timing parameters for improved RDIMM margins.

“Advanced workloads are driving an insatiable demand for greater memory bandwidth,” said Shane Rau, research vice president, Computing Semiconductors at IDC. “It’s essential that DDR5 ecosystem players like Rambus continue to raise the bar on performance to meet the rapidly rising needs of data center applications.”

“The RCD is a mission-critical enabler of DDR5 server DIMMs that provide the bandwidth and capacity needed in next-generation data centers,” said Sean Fan, chief operating officer at Rambus. “Achieving the 5600 MT/s data rate is the latest demonstration of our continued leadership in DDR5 memory interface products.”

With DDR5 memory, more intelligence is built into the DIMMs enabling up to double the data rate and four times the capacity of DDR4 DIMMs, while at the same time reducing power and increasing memory efficiency. Rambus memory interface chips are key to achieving this new level of performance for next-generation servers.

More Information:

For more information on the Rambus DDR5 RCD, please visit our website.

Rambus Delivers CXL 2.0 Controller with Industry-leading Zero-Latency IDE

Highlights:

- Offers security at speed with integrated IDE modules for unmatched performance in data center infrastructure

- Provides zero-latency data encryption for CXL.mem and CXL.cache protocols

- Integrates with Rambus CXL 2.0 PHY for complete CXL interconnect subsystem

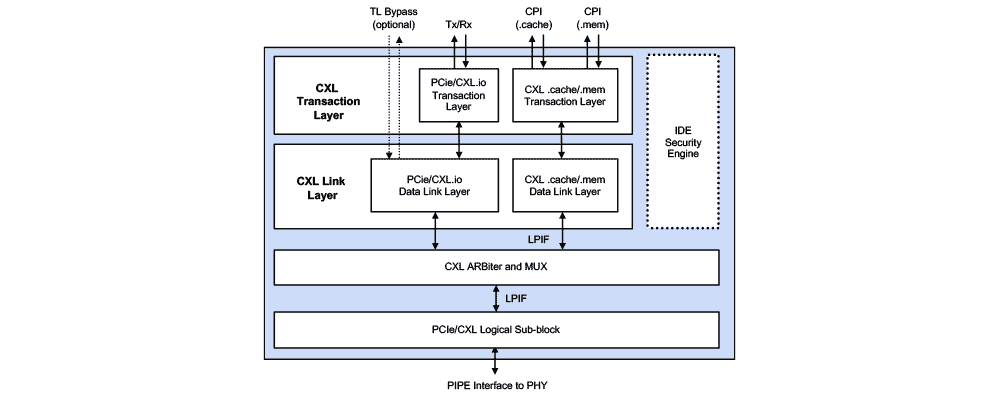

SAN JOSE, Calif. – Oct. 5, 2021 – Rambus Inc. (NASDAQ: RMBS), a premier chip and silicon IP provider making data faster and safer, today announced Compute Express Link™ (CXL) 2.0 and PCI Express® (PCIe) 5.0 controllers now available with integrated Integrity and Data Encryption (IDE) modules. Delivering security at speed in CXL is critical to solving the bandwidth bottleneck in data center infrastructure. IDE monitors and protects against physical attacks on CXL and PCIe links. CXL requires extremely low latency to enable load-store memory architectures and cache-coherent links for its targeted use cases. This breakthrough controller with a zero-latency IDE, developed by the engineering team from newly-acquired PLDA, delivers state-of-the-art security and performance at full 32 GT/s speed.

“Successful enablement of CXL use models in data-intensive applications, such as memory sharing between processors and attached AI accelerators, requires security at ultra-low latency,” said Sean Fan, chief operating officer at Rambus. “Delivering controllers with zero-latency security is a testament of our ability to accelerate the development of CXL solutions through the recent acquisition of PLDA, and showcases our unique position to provide integrated interface and security IP solutions.”

The built-in IDE modules, now available in Rambus CXL 2.0 and PCIe 5.0 controllers, employ a 256-bit AES-GCM (Advanced Encryption Standard, Galois/Counter Mode) symmetric-key cryptographic block cipher, helping chip designers and security architects to ensure confidentiality, integrity, and replay protection for traffic that travels over CXL and PCIe links. This secure functionality is especially imperative for data center computing applications including AI/ML and high performance computing (HPC).

Key features include:

- IDE security with zero latency for CXL.mem and CXL.cache

- Robust protection from physical security attacks, minimizing the safety, financial, and brand reputation risks of a security breach

- IDE modules pre-integrated in Rambus CXL 2.0 and PCIe 5.0 controllers reduce implementation risks and speed time-to-market

- Complete CXL 2.0 and PCIe 5.0 interconnect subsystems when controllers are combined with Rambus CXL 2.0 and PCIe 5.0 PHYs

More Information:

For more information on the Rambus CXL 2.0 and PCIe 5.0 controllers with integrated IDE, please visit our website:

CXL 2.0 Subsystem:

PCIe 5.0 Subsystem:

More capacity and more bandwidth: DDR5 memory enables next-generation data centers

Hear Shane Rau, Research Vice President at IDC discuss the market and technology trends surrounding the DDR5 transition, including workloads, hardware needs, market perspectives and industry timing. Joining him, John Eble, Vice President of Product Marketing at Rambus will examine the changes from DDR4 to DDR5 that are enabling more memory capacity and bandwidth critical to scaling future data centers.