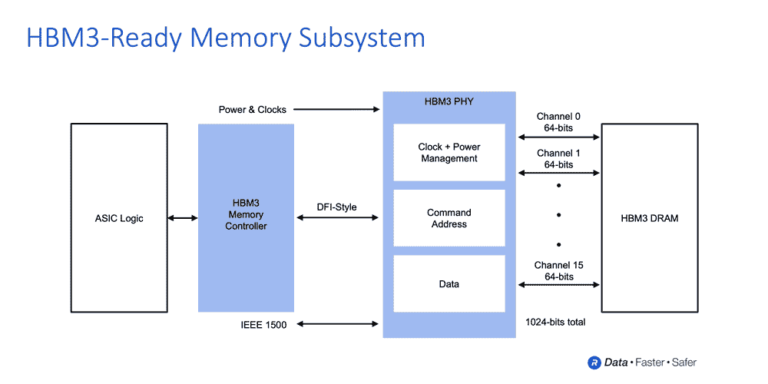

How Rambus is Making Data Faster and Safer in 2022 and Beyond

Throughout 2021 and early 2022, Rambus has continued to make data faster and safer with the launch of key products, industry initiatives, and strategic partnerships. To address the insatiable demand for more bandwidth in