TLS Toolkit is a TLS protocol implementation in C language with minimalistic system dependencies making it easily portable on any platform. Inside’s TLS Toolkit powers millions of products ranging from embedded devices with very limited capabilities to high-end network equipment.

Multi-Channel Engine MACsec-IP-163/164

The Rambus MACsec Engine supports use cases ranging from in-line encryption for single channel 1 Gbps Ethernet to 800 Gbps multi-channel Ethernet and FlexE. The MACsec-IP-164 is a high-performance MACsec frame processing engine that provides complete MACsec SecY frame transformation for multiple channels and virtual ports. It works with the MACsec-IP-163, a virtual port matching classifier, for a complete MACsec processing data path solution.

Enflame Technology Selects Rambus HBM2 Memory Subsystem Solution For Next-Generation AI Training Chip

Highlights:

- Comprehensive HBM Gen 2 (HBM2) memory subsystem solution consisting of PHY and digital controller delivers high bandwidth and low latency with minimal form factor and power envelope

- HBM2 IP provides 2Tb/s of memory bandwidth, making it the perfect fit for Enflame Technology’s cloud AI training products

- Broad suite of supporting services simplifies 2.5D integration and design with subsystem interoperability, silicon interposer and package reference designs, and signal and power integrity (SI/PI) analysis

SUNNYVALE, Calif. – Dec. 11, 2019 – Rambus Inc. (NASDAQ: RMBS) a premier silicon IP and chip provider making data faster and safer, today announced that Enflame (Suiyuan) Technology has selected Rambus HBM2 PHY and Memory Controller IP for its next-generation AI training chip. Rambus memory interface IP enables the development of high-performance, next-generation hardware for leading-edge AI applications.

“Artificial intelligence training requires far greater memory bandwidth than standard compute applications. Rambus’ proven HBM2 memory subsystem IP delivers the ultra-high bandwidth performance our AI chips need,” said Arthur Zhang, COO of Enflame Technology. “Using Rambus interface IP cores, we are revolutionizing what’s possible in AI technology.”

Optimized for low-latency and high-bandwidth memory applications, the Rambus HBM2 interface solution delivers maximum performance and flexibility in minimal form factor and power envelope. The comprehensive HBM2 subsystem solution of PHY and memory controller provides 2Tb/s of bandwidth, making it the perfect fit for Enflame Technology’s cloud AI training needs. Complementing this interface IP, Rambus provides silicon interposer and package reference designs, and supports signal and power integrity (SI/PI) analysis.

“Enflame Technology’s repeat choice of Rambus showcases our HBM2 PHY and memory controller IP as the ideal solution for complex neural network-based AI and machine learning chips,” said Hemant Dhulla, vice president and general manager of IP Cores at Rambus. “Our HBM portfolio of solutions already in volume production deliver the memory performance needed at the frontier of AI computing.”

For more information on Rambus HBM2 PHY offerings, please visit https://www.rambus.com/interface-ip/ddrn-phys/hbm/. Find out more details on Rambus Memory Controllers at https://www.rambus.com/interface-ip/controllers/memory-controllers/.

Also, check our primer:

HBM2E Implementation & Selection – The Ultimate Guide »

Rambus Completes Acquisition of the Verimatrix Silicon IP, Secure Protocols and Provisioning Business

Creates industry’s most comprehensive portfolio of silicon-proven security IP

SUNNYVALE, Calif. – Dec. 8, 2019 – Rambus Inc. (NASDAQ: RMBS), a premier silicon IP and chip provider making data faster and safer, today announced the completed acquisition of the silicon IP, secure protocols and provisioning business from Verimatrix, formerly Inside Secure, for $45 million at closing, and up to an additional $20 million, subject to certain revenue targets for the transferred business for the calendar year 2020. The combined portfolio of products, including the secure silicon IP and provisioning solutions from both companies, creates the most comprehensive silicon-proven security IP portfolio in the industry.

“This acquisition is a natural fit for the company in line with our areas of focus in semiconductor,” said Luc Seraphin, president and CEO of Rambus. “The addition of this business from Verimatrix augments our portfolio of mission-critical embedded security products and expands our offerings for data center, AI, networking and automotive.”

Although this transaction will not materially impact 2019 financial results due to the timing of close and acquisition accounting, Rambus expects this acquisition to be accretive in 2020.

For more information, visit rambus.com/insidesecure.

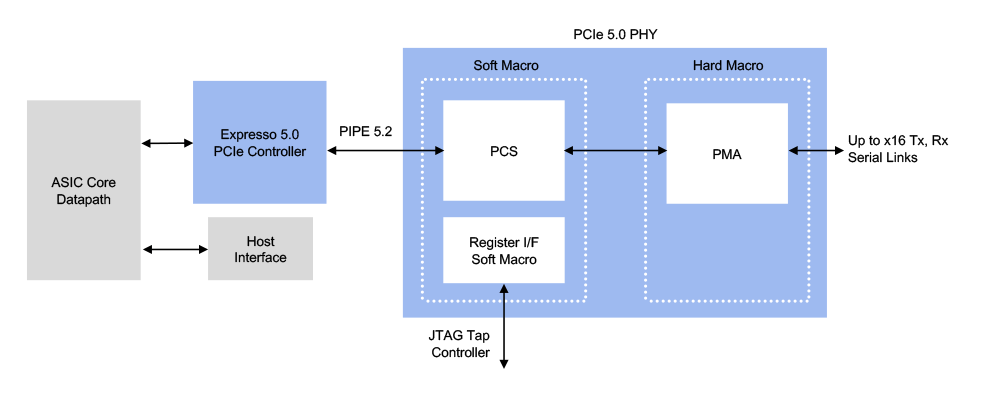

Rambus Announces Comprehensive PCI Express 5.0 Interface Solution

Highlights:

- Integrated and optimized PHY and digital controller solution enables high-bandwidth and low-latency connectivity for next-generation applications in artificial intelligence (AI), data center, high-performance computing (HPC), enterprise and cloud storage, and 400GbE networking

- PHY supports both PCIe as well Compute Express Link (CXL) connectivity between host processor and workload accelerators for heterogenous computing

- Delivers superior power, performance and area on advanced 7nm FinFET process node

SUNNYVALE, Calif. – Nov. 12, 2019 – Rambus Inc. (NASDAQ: RMBS), a premier silicon IP and chip provider making data faster and safer, today announced it now offers a comprehensive and optimized interface solution designed for PCI Express (PCIe) 5.0, with backward compatibility to PCIe 4.0, 3.0 and 2.0. The Rambus PCIe 5.0 interface solution includes both PHY and digital controller for easy SoC integration and faster time to market. With the PHY designed for an advanced 7nm process node, the integrated solution offers best-in-class power, performance and area thanks to the industry-proven engineering and signal integrity expertise of Rambus.

“Our high-speed SerDes and memory interface solutions make possible amazing advancements in performance-intensive applications in AI, data center, HPC, storage and networking,” said Hemant Dhulla, vice president and general manager of IP cores at Rambus. “Now we’ve added PCIe 5 to our industry-leading portfolio of high-speed interface solutions giving chip makers another tool to unleash the power of their designs.”

In addition to the state-of-the-art PHY, the Rambus PCIe 5.0 solution includes a high-performance, digital controller core from recently acquired Northwest Logic. The Rambus PHY and controller are offered as a fully validated and integrated solution, or they can be licensed separately and used with third-party solutions. The entire solution is backed by Rambus design, integration and support services for first-time customer success.

Benefits of Rambus PCIe 5.0 Solution

- Integrated and co-validated PHY and digital controller for complete interface solution

- Built with Rambus’ industry-proven design methodology for long-reach PCIe interfaces

- 32 GT/s bandwidth per lane with 128 GB/s bandwidth in x16 configuration

- Backward compatible to PCIe 4.0, 3.0 and 2.0

- PHY Supports Compute Express Link interconnect

- Advanced multi-tap transceiver and receiver equalization compensate for more than 36dB of insertion loss

- Best-in-class power, performance and area

- Supports performance-intensive applications including AI, data center, HPC, storage and 400GbE networking

Read our primer on our blog: Complete Interface Solution for PCI Express 5.0 Launched »

Availability and Additional Information

The new Rambus PCIe 5.0 solution is available worldwide in an advanced 7nm FinFET process.

For more information on our complete family of SerDes solutions, please visit rambus.com/serdes.

Understanding Fault Injection Attacks and Their Mitigation

Fault injection is the art of manipulating hardware behavior through voltage spikes, electromagnetic transmissions or laser impulses. Successful fault injection attacks can allow adversaries to bypass complex security and protection mechanisms entirely. Join Rambus and our partners at Riscure for a webinar explaining fault injection attacks and their mitigation.